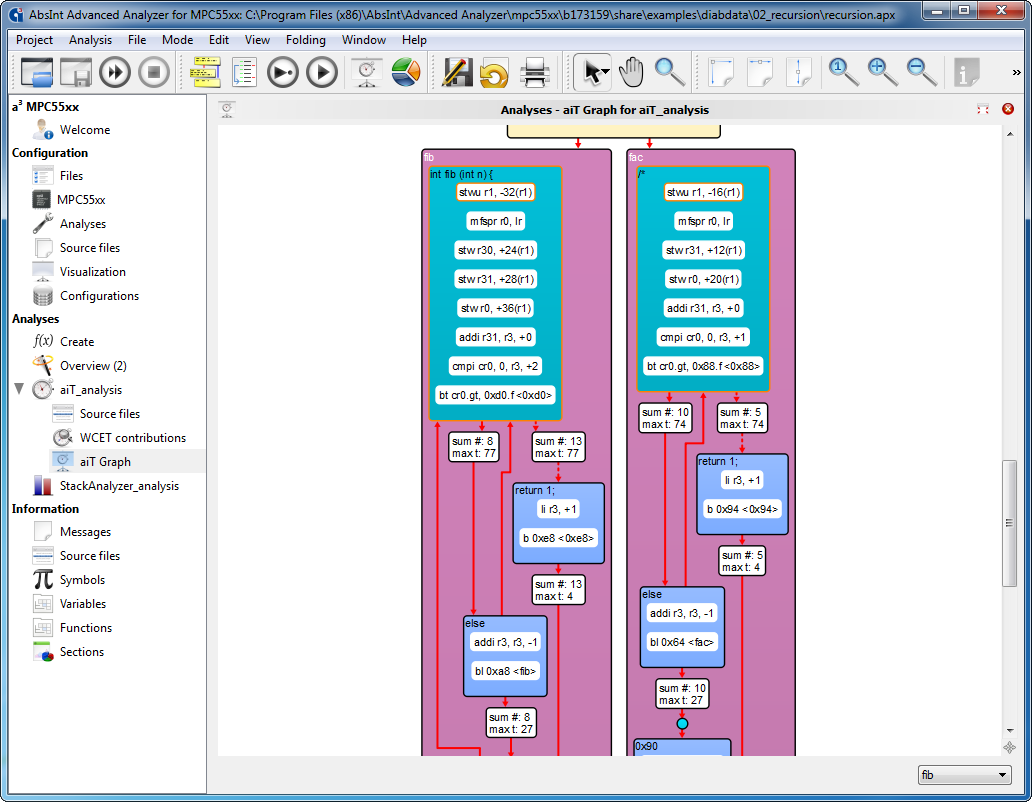

Visualization of recursions |

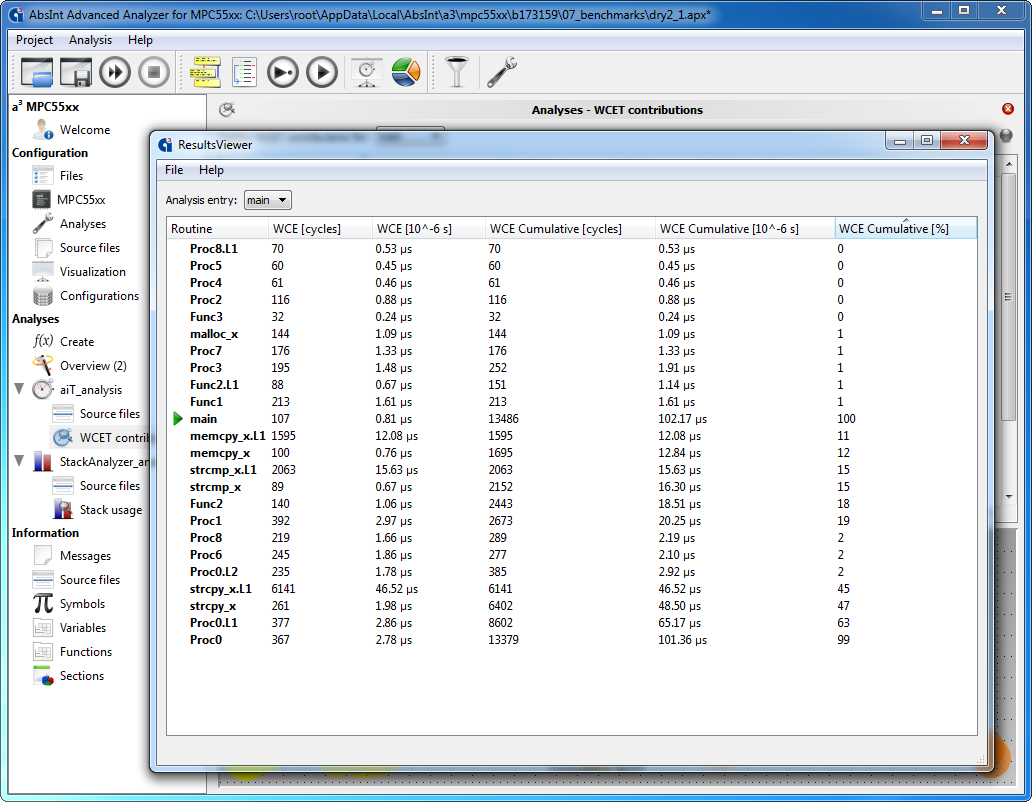

All-new Results Viewer |

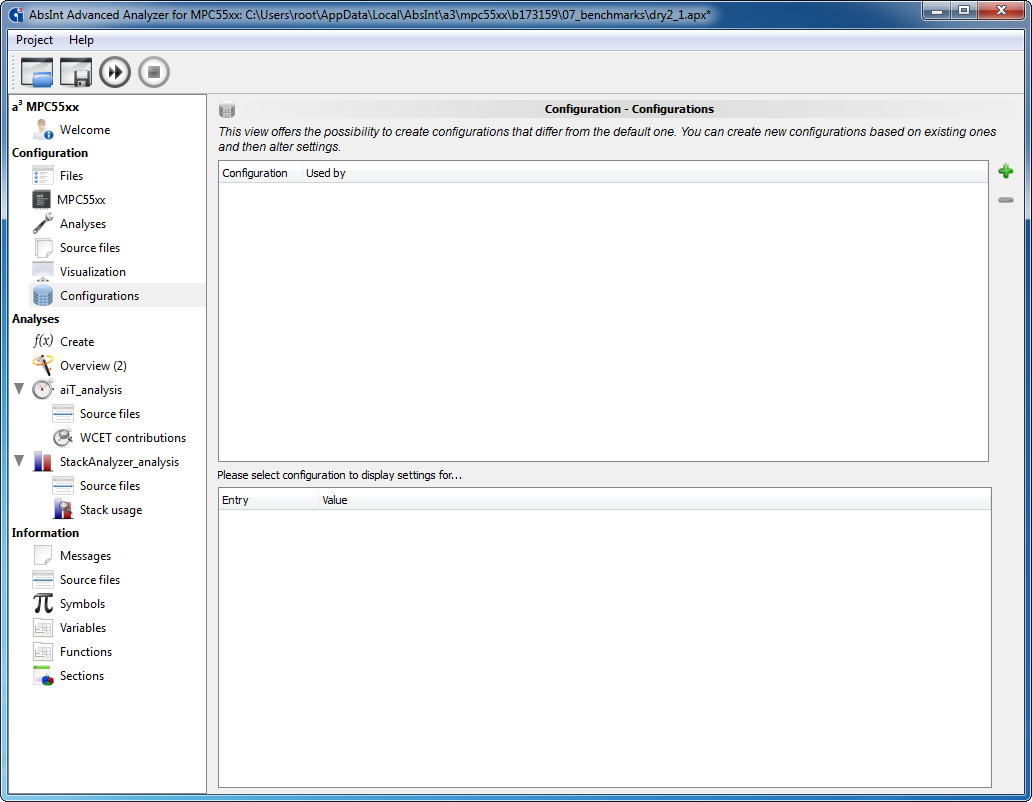

Improved Configurations view |

Targets

- aiT WCET analysis module now available for:

- aiT for M32, PCP2, and ARM7, and TimingExplorer for ARM7 have been temporarily discontinued.

Qualification Support Kits (QSKs)

- New QSK for aiT for XC2000.

- All QSKs now feature:

- an AIS expression semantics test to additionally test the

number_of_loopsfunctor; - a test for the visualization option “Use comma as decimal sign”;

- a test for the “skip n bytes at return” annotation.

- an AIS expression semantics test to additionally test the

- All aiT QSKs now include a test for the option to skip WCET analysis for the main entry in the presence of additional starts.

XTC Handling

The XTC launcher no longer closes if an analysis fails.

GUI

- Querying value analysis results in interactive mode for infeasible instructions no longer results in a GUI freeze.

- Fixed a bug that lead to message output loss or displacement of messages under Windows.

- Better handling of S-JIS encoding.

- Temporarily discontinued support for difference analysis. A revamped version will be made available in an upcoming release.

- Sped up the GUI for projects with lots of source-code debug information.

- Improved AIS Wizard.

- Better usability of links to files in the Messages view.

- Improved interactive modes for pipeline and value analysis.

- Improved usability of the Source Files view.

- Moved graph legend to the “Help” → “aiSee Graph Legend” menu.

- Pipeline and path analysis can be disabled for the main entry point if additional entry points are being analyzed.

- Improved Configurations view.

- Filter dialogs now remember the last filter string.

- Minor improvements to the Sections view.

- An all-new Results Viewer provides an additional view of the analysis results.

- Improved encoding detection in the text editor.

- Improved “Show address in call graph” navigation between the Messages and the Graph view.

- Improved XTC handling.

- Interactive value analysis will show target address of the outgoing edges.

AIS

- Introduced special variable

number_of_loopsfor use in expressions at any program point P evaluating to the number of loops contained in the routine containing P. - Extended the annotation “

ROUTINE R1 CALLS TO R2 INCARNATES <X>;” to catch indirect calls from the call stack when the boundXequals zero. With this extension it is possible to express thatR2becomes infeasible iff there is a path fromR1toR2. - AIS annotations via file and line now work even if the corresponding source file is not available.

- AIS annotations will only be extracted from source files referenced in debug information.

- Introduced annotation to skip some bytes after call return.

- Improved handling of the “

snippet <PP1> continuing <PP2>,...” annotation.

Decoding

- Any section without a name now gets the default name

:Section_<start address>, enabling it to be used in annotations. - Loop type will be detected in many cases. The user is informed about wrong begin/end loop annotations.

- Search source files not from directory of executable, but from directory of project file.

- Improved reporting of found strongly-connected components (SCCs).

- ARM:

- Fixed the handling of the AIS keyword

trapfor software interrupt annotations. - Now fully supporting the ARM Greenhills compiler.

- General improvements to the decoding of ARM binaries.

- Improved support for the TI C/C++ compiler v4.4.16:

- New return patterns.

- Automatic handling for compiler introduced tail call optimization. Generated routines are automatically recognized as immediately returns.

- Fixed the handling of the AIS keyword

- HCS12:

- Decoder now features the iterative decoding strategy introduced in 11.08.

- Improved handling of EMACS, MAXA, MAXM, MINA, MINM, and MEM instructions.

- M68020:

- Improved decoding of

fmod/freminstructions. - Correct decoding of

dbccwithcc == true(no branch, just a fall-through to the successor).

- Improved decoding of

- PPC: guessed stackpointer is now always 8-byte aligned according to processor ABI.

- SPARC:

- Improved decoding of binaries.

- Better handling of annulled delay slots. Control flow graph is changed to move them only to the true case of the branch.

- Guessed stackpointer is now always 8-byte aligned according to processor ABI.

- Improved tail call detection.

- X86: improved switch table resolving.

Stack, loop, and value analysis

- Improved loop analysis of nested loops.

- Adjusted the behavior of the “access default” annotation.

- Handle loops with too large unrolling, the limit is 224 − 1. Now instead of an error, the unrolling is limited to maximal amount.

- Better output of accesses to watched areas: more structure and less duplicate information.

- The value analysis now tries to give hints about possible targets of computed calls.

- The annotation “is entered with rx = value” now only allows improving the computed register content. If the annotation conflicts with the computed value, the path with the contradiction will be marked as infeasible and a warning will be issued.

- The value analyzer now references a register-modifying annotation that leads to a conflict during value analysis.

- Improved loop bound detection for all three kinds of loop annotations:

loop "x" max 5;loop "x" max 5 by default;global loop iteration default max 5;

For 1. and 2., the bound provided by the user is intersected with the bound computed by the loop analysis. If the intersection is empty, the loop is marked infeasible and an error is issued. If the computed bound is detected as unsafe, it is silently discarded and the user annotation is taken instead, without any intersection. The report file contains information about how the final bound is derived (i.e. whether it is the result of a user annotation, auto-detection or both).

For 1., it no longer makes a difference if a constant term or an expression is used.

Type 3 annotations will be ignored during loop/value analysis and only applied during path analysis (no unrolling is done with this bound).

- Improved precision for overlapping memory writes.

- ARM: improved StackAnalyzer support for ARM v5 ISA.

- HCS12:

- Modifications of PPAGE are now supported.

- Improved loop-bound detection for the Hiware compiler.

- Improved handling of EMACS, MAXA, MAXM, MINA, MINM, MEM and PC-relative MOVB/MOVW instructions.

- M68020: improved handling of complex addressing modes and

dbccandrte/rtrinstructions. - PowerPC:

- Added support for the

mbarinstruction (stack analysis only). - Corrected semantics of the VLE rotate instruction in some special cases.

- Corrected semantics of the

stwbrxinstruction.

- Added support for the

- SPARC (ERC32/LEON2/LEON3):

- More loop patterns and better loop-bound detection.

- Better handling of annulled delay slots.

- TriCore: improved handling of TriCore addressing modes

brevandcirc.

Path analysis

- Improved analysis precision and speed.

- Analysis of indirect recursions needs max-length of at least recursions depth.

Cache and pipeline analysis

- LEON2/LEON3:

- Improved handling of atomic load/store instructions.

- Improved handling of delay slot instruction execution of annulled conditional branches, whose branch condition evaluates to true.

- MPC5xx:

- Improved handling of tail instructions.

- Faster pipeline analysis.

- MPC55xx: implemented persistence analysis for the pipeline analysis.

- MPC7448: improved early state split.

- MPC755s/MPC7448s: implemented a highly configurable and generic memory controller interface unit that is able to simulate static RAM, DDR/SD RAM and PCI accesses.

- TriCore:

- Improve TriCore Pipeline Local-WCET mode.

- Emit error message for unsupported cache manipulating instructions.

- V850: correct handling of "callt" instruction in v850e1f pipeline analysis.

- Useful cache block (UCB) analysis for MPC55xx/MPC56xx/MPC603/LEON2:

- Prediction-file based UCB analysis "pucban" replaces old UCB analysis "ucban". The new analysis gives a major increase in analysis performance and significantly reduced memory consumption.

- Implemented UCB analysis for LEON2.

Visualization and reporting

- Display the name of additional start routines in graph visualization.

- Routines or basic blocks that are infeasible are no longer marked with a red border if they contain unresolved computed calls.

- Visualization of recursions and routines inside a strongly-connected component.