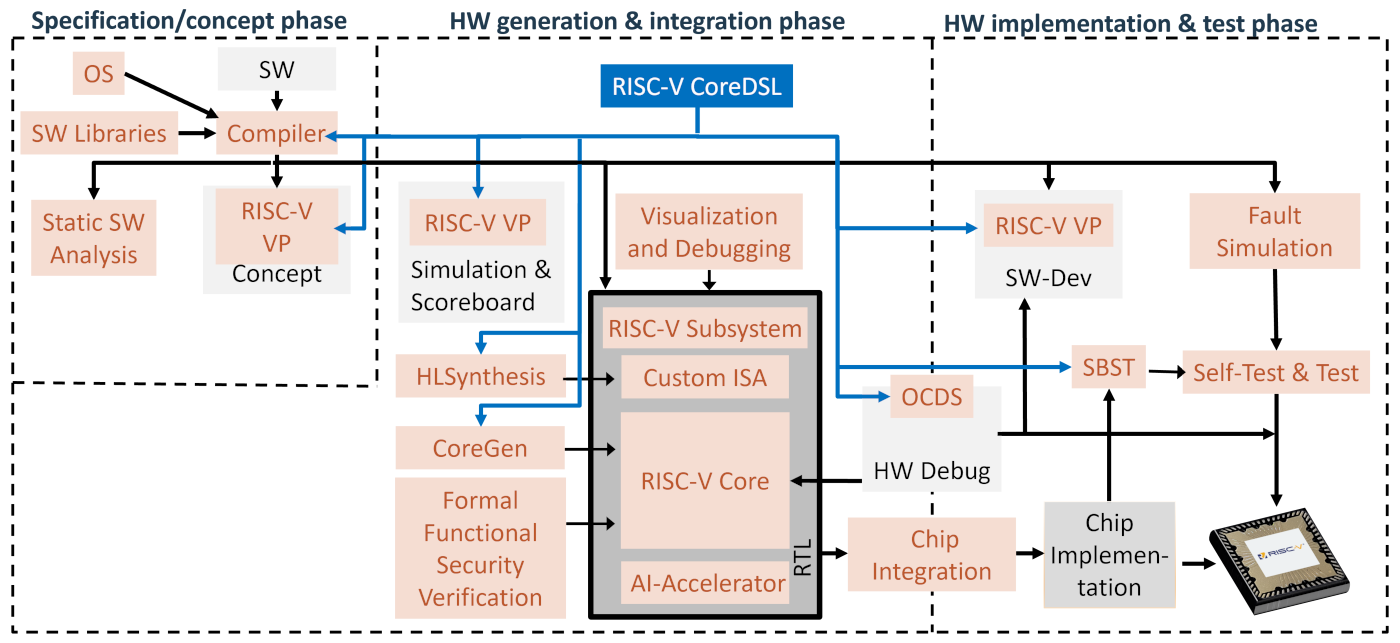

TRISTAN

Together for RISC-V Technology and Applications

A multinational EU-funded project that aims to expand and develop

the RISC-V architecture such that it can better compete

with existing commercial alternatives. The TRISTAN approach

is holistic, covering design automation tools

and the full software stack. A multitude of demonstrators are

likewise being developed, including nano drones with exceptional stealth

and agility, a RISC-based high-performance control algorithm for BLDC motors,

and robotic algorithms to be virtually deployed in an autonomous

driving testing environment through synthetically generated data.

Our contribution includes developing a custom version of TimeWeaver

for RISC-V and extending CompCert

to support the TRISTAN HSI interface.

Consortium:

NXP,

Infineon,

ST Microelecronics,

CEA,

Bosch,

Thales,

Leonardo,

Siemens,

MinRes,

Technolution, AntMicro,

SYSGO,

AbsInt,

Nokia, the Royal Netherlands Aerospace Center, Yonga,

Eclipse Foundation,

EPOS,

Tampereen, Cargotec, CodaSip, aicas,

VLSI Solution, Tensor Embedded, Irdeto,

E4 Computer Engineering, Strohmayer Klaus,

Accemic,

Greenwaves Technologies, IMEC, Fraunhofer, Synthara,

Universities of Twente, Turin, and Bologna, TUs of Munich, Darmstadt, Graz, and Zurich.

Consortium:

NXP,

Infineon,

ST Microelecronics,

CEA,

Bosch,

Thales,

Leonardo,

Siemens,

MinRes,

Technolution, AntMicro,

SYSGO,

AbsInt,

Nokia, the Royal Netherlands Aerospace Center, Yonga,

Eclipse Foundation,

EPOS,

Tampereen, Cargotec, CodaSip, aicas,

VLSI Solution, Tensor Embedded, Irdeto,

E4 Computer Engineering, Strohmayer Klaus,

Accemic,

Greenwaves Technologies, IMEC, Fraunhofer, Synthara,

Universities of Twente, Turin, and Bologna, TUs of Munich, Darmstadt, Graz, and Zurich.

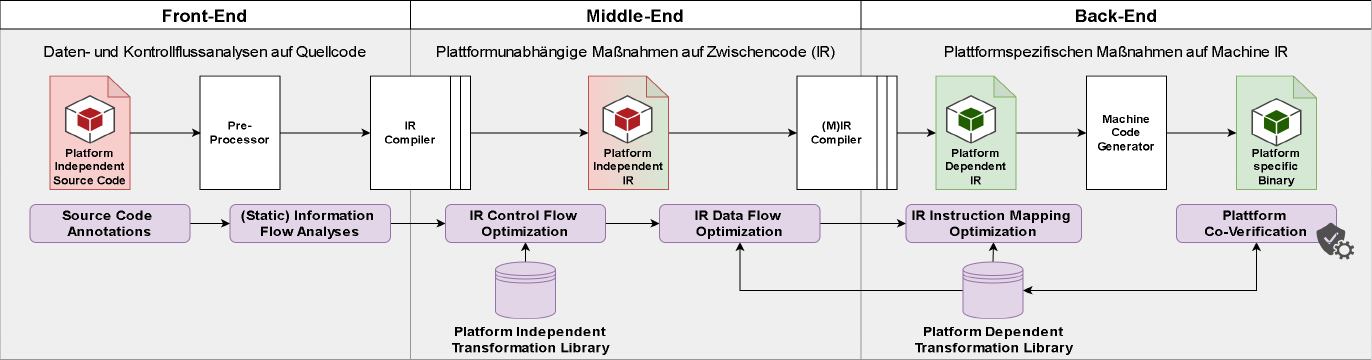

Scale4Edge

Scalable Infrastructure for Edge Computing

This project aims to strengthen the technology sovereignty in Germany,

starting with the competence of German companies and universities

in the field of processor technology and the associated supply chains

for various edge applications. This will result in new processor

architectures, innovative software, and special verification approaches,

thus strengthening technology sovereignty for the entire ecosystem.

As a specific use case, Bosch developed a neural-network based

audio-event detection model, which has been ported to a Pulpissimo-based

SoC platform using components and software of the Scale4Edge ecosystem.

Our contribution includes adapting the CompCert

compiler for the RISC-V architecture.

Consortium:

Infineon,

Altair,

DLR,

Bosch,

FZI,

EPOS,

SYSGO,

AbsInt, IHP,

MinRes,

HM Munich, Universities of Darmstadt, Dresden, Munich, Bremen, Paderborn,

Freiburg, Tuebingen, and

Kaiserslautern.

Consortium:

Infineon,

Altair,

DLR,

Bosch,

FZI,

EPOS,

SYSGO,

AbsInt, IHP,

MinRes,

HM Munich, Universities of Darmstadt, Dresden, Munich, Bremen, Paderborn,

Freiburg, Tuebingen, and

Kaiserslautern.

FreeSBee

Side-Channel-Free Software for Embedded Systems

Funded by the German Ministry of Research, Technology, and Space,

this project is developing tool-assisted methods for automated

recognition and rectification of security flaws in embedded systems

that can be exploited for side-channel attacks.

Consortium:

AbsInt,

FZI,

Kasper & Oswald.

Consortium:

AbsInt,

FZI,

Kasper & Oswald.

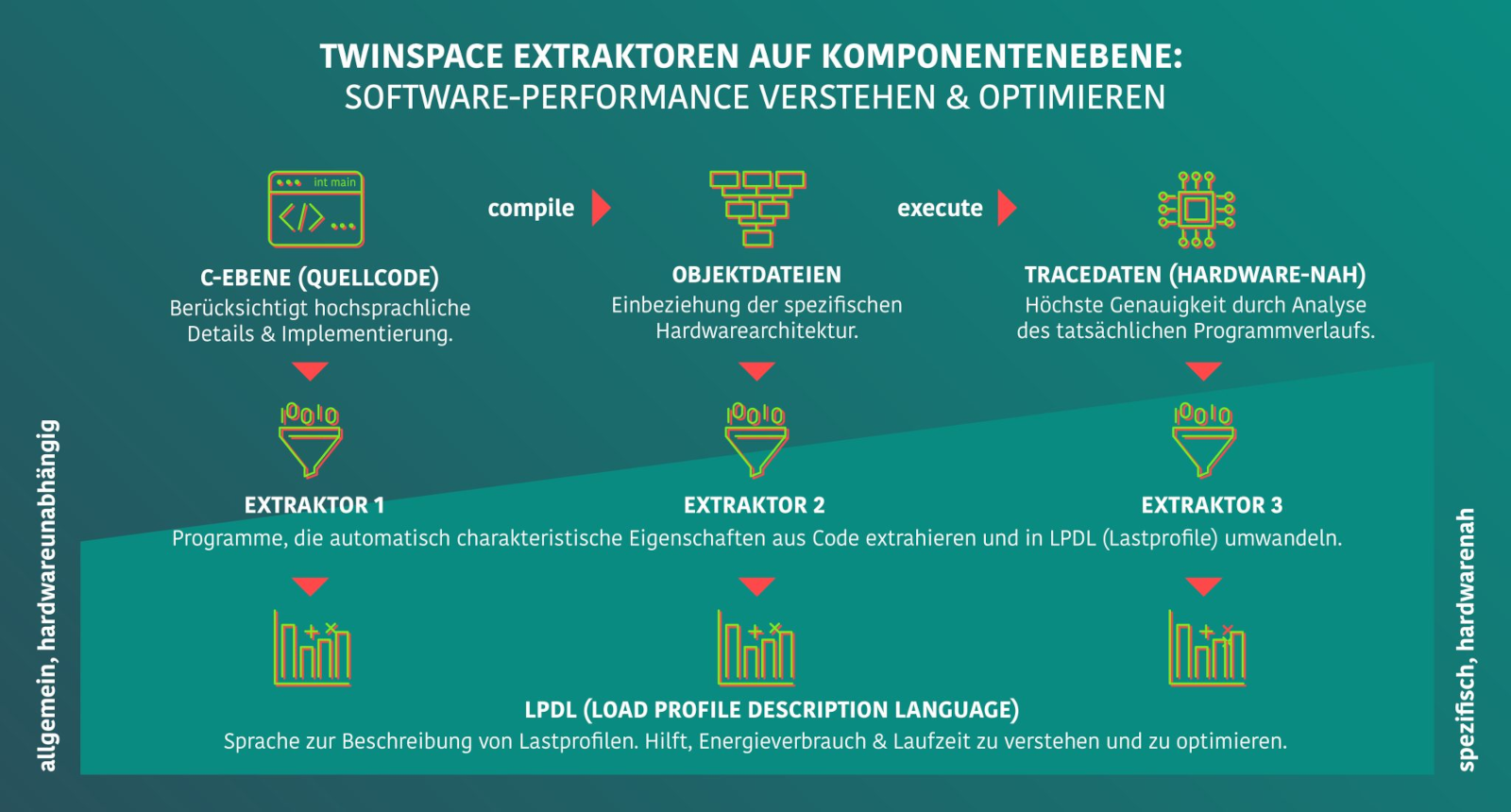

TwinSpace

Resource-Coupled Hardware–Software Co-Design

This project is working on an integrated solution for the co-design of hardware

and software that simulates the resource usage of software systems during their development,

even at early design stages. Thanks to an innovative combination

of automated reverse engineering and simulated hardware-platform tests,

highly optimized code can be produced for each specific hardware configuration.

This makes the development process fully transparent from the get-go,

accelerates and simplifies the integration of new software components,

and helps achieve a previously unseen balance between the economic benefits

and the ecological sustainability of safety-relevant software systems.

Consortium: EFS, CARIAD, AbsInt,

emmtrix,

Tensor Embedded,

SYSGO,

NXP,

Universities of Augsburg, Luebeck, Clausthal, and Cottbus-Senftenberg.

Consortium: EFS, CARIAD, AbsInt,

emmtrix,

Tensor Embedded,

SYSGO,

NXP,

Universities of Augsburg, Luebeck, Clausthal, and Cottbus-Senftenberg.

2026

2025

2024

2023

2022

2021

2020

2019

2018

2017

2016

2015

2014

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

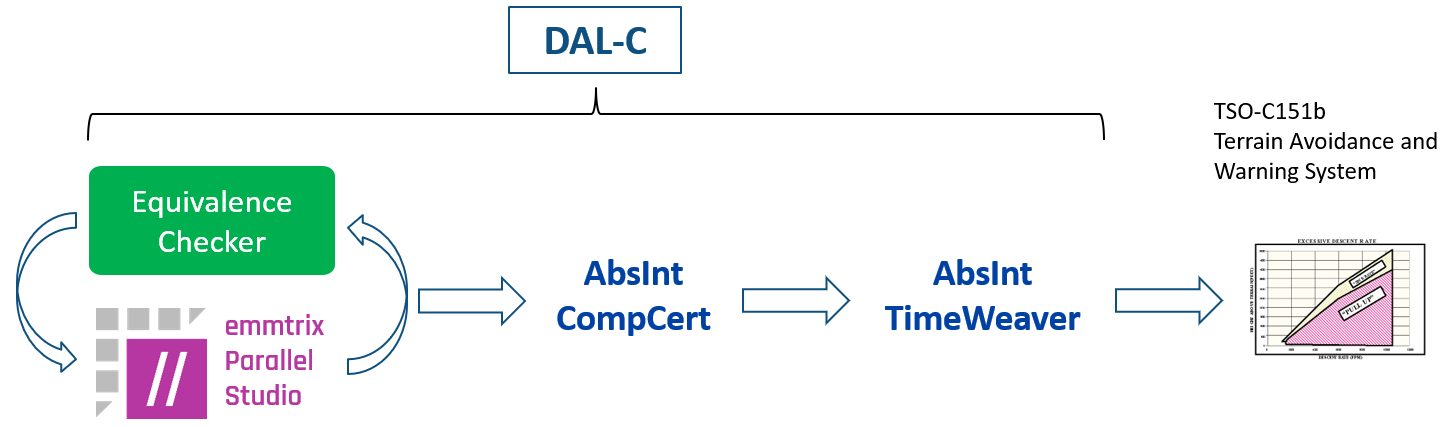

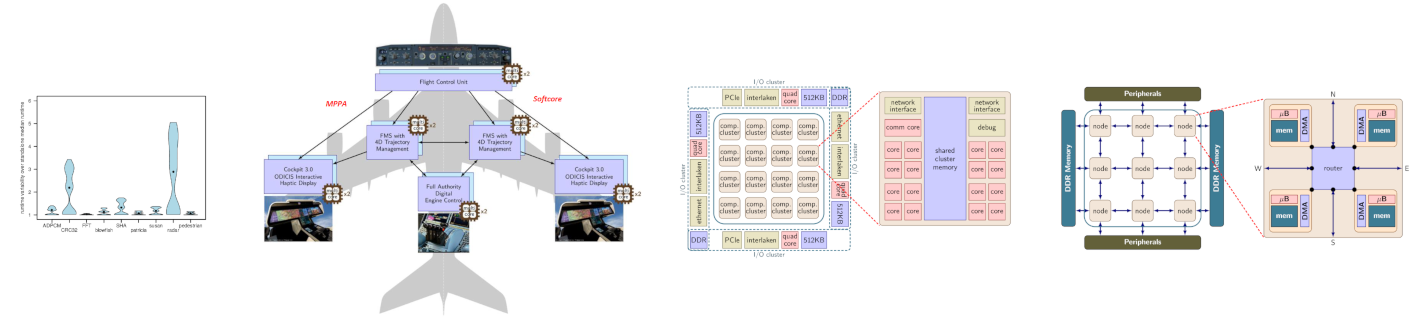

QSMA

Qualifiable Software Parallelization for Multicore Avionics Systems

A civil-aviation project by the German Federal Ministry for Economic Affairs and Energy

that established a DO-178C/DO-330 qualifiable toolchain for multicore software

development that includes CompCert and TimeWeaver.

For demonstration, the toolchain was used to develop a TSO-C151b Terrain Avoidance

and Warning System in accordance with DAL-C.

Consortium:

emmtrix,

DLR,

AbsInt, TU Clausthal, Validas.

Consortium:

emmtrix,

DLR,

AbsInt, TU Clausthal, Validas.

MORAL

Export-Free Rad-Hard Microcontroller for Space Applications

This project developed a completely European, ITAR-free microcontroller

for space applications, with a focus on small satellites,

flight control and payload computers, and tasks such as mission control,

Earth observation, and navigation. The microcontroller offers

increased reliability and adaptability to the needs of space applications.

In addition to the hardware, the required ITAR-free middleware,

RTOS and toolchain have been made available.

Consortium:

IHP,

SYSGO,

AbsInt, RedCat Devices,

Thales Alenia Space.

Consortium:

IHP,

SYSGO,

AbsInt, RedCat Devices,

Thales Alenia Space.

TeamPlay

Time, Energy, and Security Analysis for Multi- and Many-Core Heterogeneous Platforms

This project developed new formal techniques that allow execution time, energy usage, security, and other non-functional properties of parallel software to be treated as first-class citizens. The project brought together leading industrial and academic experts in parallelism, energy modeling, worst-case execution time analysis, non-functional property analysis, compilation, security, and task coordination. Results were evaluated using industrial use cases from the domains of computer vision, satellites, flying drones, medicine and cybersecurity. The three-year project was funded by the EU Horizon 2020 research and innovation programme. Our contribution included the development of EnergyAnalyzer.

Consortium: INRIA, Thales Alenia Space, Sky-Watch, IRIDA Labs, AbsInt, Universities of Amsterdam, Hamburg, Bristol, St. Andrews, and Southern Denmark.

EMPHYSIS

Embedded Systems with Physical Models in the Production-Code Software

2021 ITEA Award of Excellence, Special Vice-Chairman’s Award.

In this project, 26 partners from five countries developed a new open standard, eFMI, to exchange physics-based models between high-level modeling and simulation environments and low-level development tools for embedded code. The standard captures functional and non-functional quality requirements, supports traceability, and enables semi-automatic generation of code that is 25% faster than state-of-the-art handwritten code. The project additionally produced 33 use cases, 40 simulation configurations, and 13 tool prototypes.

Consortium: Bosch, Siemens, Volvo, Renault, Dassault, Maplesoft, CEA, Dana Belgium, FH Electronics, Grenoble INP, OSE Engineering, SOBEN, DLR, AbsInt, dSPACE, ETAS, ESI ITI, e:fs, PikeTec, Autoliv, RISE, Modelon, Universities of Linköping and Antwerp.

PROFORMA

Formal Analysis of the Propagation of Spurious Hardware Errors

Funded by the German Federal Ministry of Education and Research, this project investigated the effects of hardware errors on software. These included single-event upsets that manifest themselves via bit flips in memory cells and registers. PROFORMA worked on models, techniques, and automatic tool chains that enable developers to formally prove whether or not hardware errors will affect particular tasks or functionality. Among other things, our contribution included extending the static analyzer Astrée to support taint analysis.

Consortium: AbsInt, TU Kaiserslautern, Verified Systems International.

AQUAS

Aggregated Quality Assurance for Systems

This project investigated the challenges arising from the interdependence of safety, security and performance of safety-critical systems in transportation, medicine, space, and industrial control. AQUAS aimed at efficient solutions for the entire product life cycle, and devised a coordinated engineering approach to address the ever-growing requirements on security and performance, while maintaining safety. Our contribution included combining safety analysis in the design phase with WCET analysis in the implementation phase, performing TimingProfiler analyses of Thales Alenia Space software, and using the static analyzer Astrée to analyze SYSGO’s PikeOS operating system.

Consortium: CEA, Thales, Thales Alenia Space, Siemens, Ansys Medini, RGB Medical Devices, SYSGO, AbsInt, All4tec, Clearsy, Brno University of Technology, Austrian Institute of Technology, Tecnalia, ITI, Intecs, Telecom ParisTech, TrustPort, Magillem, Integrasys, RheinMain University of Applied Sciences, Universities of London and L’Aquila.

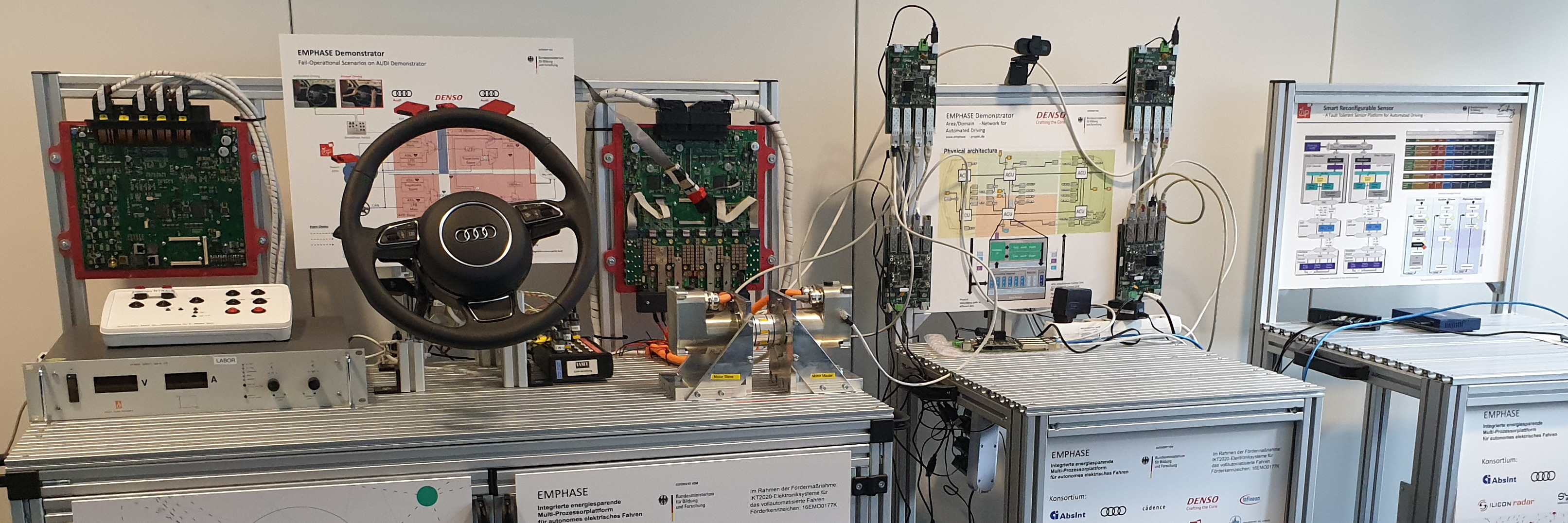

EMPHASE

Integrated Energy-Saving Multi-Processor Platform for Autonomous Electric Driving

Funded by the German Federal Ministry of Education and Research,

this project developed an energy-efficient computer system for processing

sensor data in automated vehicles.

Consortium:

Audi,

DENSO,

Infineon,

Silicon Radar,

SYSGO,

AbsInt, Cadence, IHP, TU Brunswick.

ARAMiS II

A follow-up to the ARAMiS project. This time, the focus lay on optimization and advancement of the development processes, especially tools and platforms for the efficient usage of multicore technology. The applicability of all concepts and approaches was put to the test in industrial use cases from the automotive, avionics and industry automation domains. The three-year project was sponsored by the German Federal Ministry of Education and Research.

Consortium: DLR, Audi, Bosch, Continental, DENSO, Schaeffler, Airbus, General Electric, Hensoldt, Diehl Aerospace, Liebherr Aerospace, Siemens, WIKA Mobile Control, KSB, AbsInt, Accemic, ElektroBit, OpenSynergy, Silexica, Symtavision, Vector, Fraunhofer, KIT, OFFIS, ISP, fortiss, Universities of Augsburg and Kiel, TUs of Brunswick, Kaiserslautern, and Munich.

ARGO

WCET-Aware Parallelization of Model-Based Applications for Heterogeneous Parallel Systems

This project developed a holistic approach for programming heterogeneous multicore and many-core architectures using automatic parallelization of model-based real-time applications. ARGO enhanced WCET-aware automatic parallelization by a cross-layer programming approach combining automatic tool-based and user-guided parallelization, thus reducing the need for expertise in programming parallel heterogeneous architectures. Among other things, our contribution included porting our flagship product aiT to Xentium, as well as supplying aiT for LEON3 with a memory-access counting extension.

Consortium: KIT, DLR, Dassault, Fraunhofer, TEU of Western Greece, emmtrix, AbsInt, University of Rennes 1.

ASSUME

Affordable Safe and Secure Mobility Evolution

In this project, 38 partners from five countries devised an affordable and safe multicore engineering methodology that allows the industry to develop mobility solutions with trustworthy new functions at competitive prices. Our contribution included improving the usability of the formally verified CompCert compiler, raising the precision and efficiency of the static analyzer Astrée, extending the aiT WCET Analyzer to support the analysis of code running on the second generation of the Kalray MPPA processor, and extending Astrée to support AUTOSAR supplementary libraries, real-time POSIX, and sound analysis of data races and deadlocks.

Consortium: INRIA, Airbus, ENS, Esterel, Kalray, Thales, Safran (Snecma), Safran (Sagem), Daimler, BTC, Expleo, FZI, KIT, Model Engineering, OFFIS, Bosch, AbsInt, NXP, Recore, TNO, VDL, Verum Software, Arcticus, FindOut, KTH, Scania, Arçelik, Ericsson, Ford, Havelsan, KoçSistem, UNIT, Universities of Sorbonne, Kiel, Munich, Eindhoven, Twente, and Mälardalen.

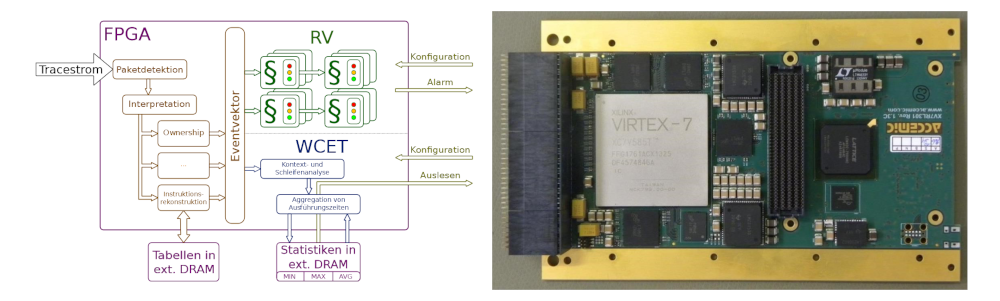

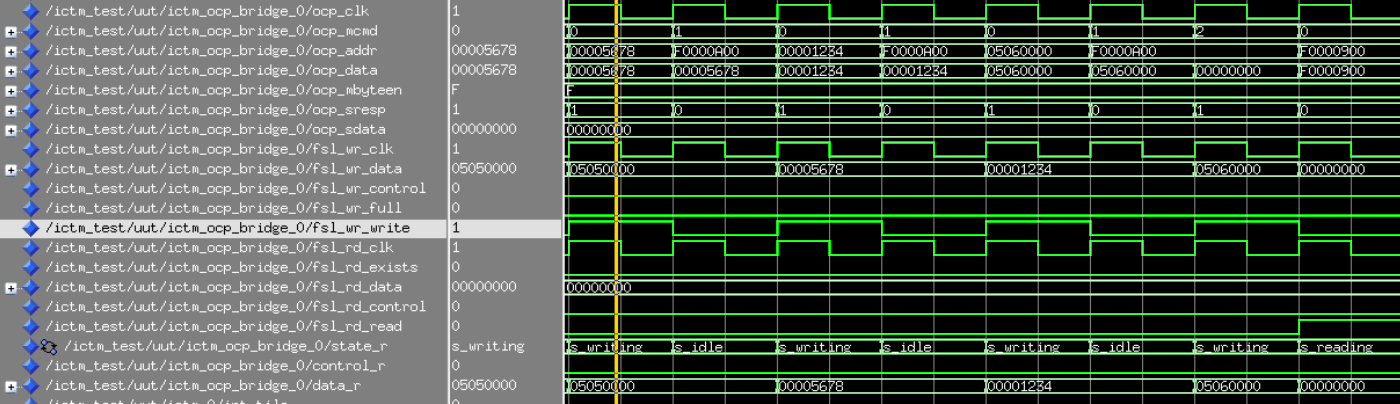

CONIRAS

Continuous Non-Intrusive Runtime Analysis of Systems-on-Chip

With the aid of an all-new debugging system, this project

collected and analyzed trace data in real time. To that end,

an FPGA platform and several specialized synthesis applications

were developed. The work was funded by the German Federal Ministry

of Education and Research.

Consortium: AbsInt, Accemic, TU Darmstadt, University of Luebeck.

Consortium: AbsInt, Accemic, TU Darmstadt, University of Luebeck.

FORTISSIMO

Formal Techniques for Embedded Systems

A mid-term project funded by the German Federal Ministry of Education and Research. A follow-up to the FORTE project, this time focusing on verification of concurrent systems.

Consortium: AbsInt, OneSpin Solutions, TU Kaiserslautern.

CERTAINTY

Certification of Real-Time Applications Designed for Mixed Criticality

This project worked out a methodology

for the development of complex critical applications,

notably for many-core and multicore processors. This included

a DOL-critical tool chain, Network-on-Chip tools, a code-generation tool

chain for Kalray MPPA, and runtime environment tools.

Our contribution included adapting our flagship product aiT

for the MicroBlaze architecture. The project was funded by the European

Commission under the 7th Framework Programme for Information and

Communications Technologies.

Consortium:

Thales,

Kalray, ARTTIC, Université Joseph Fourier,

AbsInt, ETH Zurich, Uppsala University, TU Brunswick.

Consortium:

Thales,

Kalray, ARTTIC, Université Joseph Fourier,

AbsInt, ETH Zurich, Uppsala University, TU Brunswick.

ARAMiS

Funded by the German Federal Ministry of Education and Research, this research project demonstrated the usability of multicore technology in safety-critical applications and improved the technological basis for increased safety, efficiency, and comfort in the automotive, avionics, and rail transportation domains. Our contribution included developing a new static analysis type for multi-core architectures, to automatically recognize accesses to shared resources.

Consortium: KIT, Audi, BMW, Bosch, Continental, Daimler, Airbus, Symtavision, SYSGO, Vector, AbsInt, OFFIS, and 18 others.

T-CREST

Time-Predictable Multi-Core Architecture for Embedded Systems

This project devised and built a system that prevents delays

in the execution of safety-critical software, lowers

development costs and reduces complexity.

Our contribution included adapting aiT WCET Analyzers

for the Patmos architecture. The project was

partially funded by the European Commission under the 7th Framework

Programme for Information and Communications Technologies.

Consortium:

The Open Group, TU Denmark, AbsInt, GMV, Intecs,

TU Eindhoven,

TU Vienna,

University of York.

Consortium:

The Open Group, TU Denmark, AbsInt, GMV, Intecs,

TU Eindhoven,

TU Vienna,

University of York.

MBAT

This project enabled effective and efficient validation and verification of embedded systems, by combining advanced model-based testing technologies with static analysis and verification techniques. Led by Daimler and funded by the European ARTEMIS Joint Undertaking, the project brought together 39 partners from nine countries.

Consortium: Daimler, Airbus, Infineon, IBM, Thales, Dassault, Volvo, Siemens, CEA, ENS, Fraunhofer, BTC, ENEA, PikeTec, MBtech, OFFIS, Ansaldo, Leonardo, Selex, Ricardo, ALES, AMET, AVL LIST, All4tec, Alstom, Elvior, Alenia Aermacchi, Alten, Virtual Vehicle Research, KTH, Austrian Institute of Technology, Universities of Aalborg and Mälardalen, TUs of Munich and Graz.

FORTE

Formal Techniques for Embedded Systems

A mid-term project funded by the German Federal Ministry of Education and Research. It improved and integrated the project partners’ formal verification techniques for C and VHDL programs, thus increasing the overall benefit of formal verification, especially for the automotive industry.

Consortium: AbsInt, TU Kaiserslautern.

artist2

Network of Excellence in Embedded Systems Design

This project established a unique European virtual center of excellence, combining competencies from electrical engineering, computer science, applied mathematics and control theory, and covering all aspects of embedded-systems design from theory through to applications.

Our cluster: Compilers and Timing Analysis

Partners: ST Microelecronics, AbsInt, TU Vienna, RWTH Aachen, Universities of Mälardalen, Saarland, Dortmund and York.

TIMMO-2-USE

Timing Model — Tools, Algorithms, Languages, Methodology, Use Cases

This project addressed the specification, transition and exchange of relevant timing information throughout different steps of the AUTOSAR-based development process and tool chain. This was achieved using the Timing Augmented Description Language, TADL2, that offers capabilities for symbolic time expressions modeling, probabilistic timing information, and timing constraints applied on mode definitions and aligned with EAST-ADL and AUTOSAR timing models. Our contribution included integrating the aiT WCET Analyzers and the static analyzer Astrée with TargetLink from dSPACE.

Consortium: Volvo, INRIA, Delphi, Continental, Bosch, Rapita Systems, Arcticus, dSPACE, AbsInt, Symtavision, Inchron, RealTime-at-Work, Time Critical Networks, Chalmers University of Technology, Universities of Brunswick, Paderborn, and Mälardalen.

CESAR

Cost-Efficient Methods and Processes for Safety-Relevant Embedded Systems

This European-funded project from the ARTEMIS Joint Undertaking boosted the cost efficiency of embedded-system development, safety processes, and certification. CESAR pursued a multi-domain approach, integrating large enterprises, suppliers, SMEs, vendors of cross-sectoral domains, and leading research organizations.

Consortium: AVL LIST, Airbus, Infineon, DLR, Thales, Safran, Siemens, ABB, Hitachi, Volvo, Fiat, Delphi, Dassault, Esterel, CEA, CNRS, INRIA, ONERA, Selex, NTNU, KTH, SINTEF, BTC Embedded Systems, Fraunhofer, AbsInt, OFFIS, alenia, Danieli Automation, Virtual Vehicle Research, Critical Software, Acciona Construccion, Tecnalia, Auvation Software, Hellenic Aerospace Industry, Universities of Oxford, Manchester, Athens, Thessaloniki, Trieste, and Bologna.

Partner up with us

Contribute your expertise. Benefit from ours. Get in touch.

PREDATOR

Design for Predictability and Efficiency

A three-year focused-research project within the European Commission’s 7th Framework Programme on Research, Technological Development and Demonstration. Steered by Airbus and Bosch, the project improved the design and development methods for safety-critical embedded systems, by formalizing architectural concepts that support the derivation of timing guarantees for hard real-time systems, and providing the corresponding architectural platforms. Our contribution included extending the aiT WCET Analyzer with UCB (Useful Cache Block) analysis, and extending the XTC (XML Timing Cookies) format to allow the transfer of UCB analysis results and cache-content information to scheduling tools.

Consortium: Saarland University, Swiss Federal Institute of Technology, TU Dortmund, University of Bologna, Scuola Superiore Sant’Anna, AbsInt, EADS Airbus, Bosch.

Interested

A follow-up to Interest, within European Commission’s 7th Framework Programme on Research, Technological Development and Demonstration. This time the project partners created an open interoperable toolchain that fulfills the needs of the industry for designing and prototyping embedded systems. 17 interfaces between 11 tools were implemented, enabling the creation of 14 new product prototypes already before the project was completed.

Consortium:

SYSGO,

Symtavision, AbsInt,

CEA,

Esterel, Atego, Evidence, TTTech.

The work results were evaluated by industrial partners that included

Airbus,

Thales,

Magneti Marelli, and Siemens Rail Automation.

In the final project report, Airbus stated that its use of the Interested

toolchain resulted in a 48% reduction in overall project effort.

Thales reported a 25% reduction in effort, and Siemens

reduced project costs by 20%. CEA’s initial development costs

were reduced by 40% and ongoing maintenance costs by 69%,

while Magneti Marelli reported a 50% time saving.

COLA

Cache Optimizations for LEON Analyses

A research project funded by the European Space Agency ESA under the basic Technology Research Programme, and a follow-up project to PEAL2 (Prototype Execution-time Analyser for LEON). This time, the project partners investigated how software running on a processor with cache can achieve maximum performance while remaining testable, predictable and analyzable. The work was done with particular reference to the LEON, which is widely used in space applications. Our contribution included porting our flagship product aiT WCET Analyzer to support LEON.

Consortium: University of Padua, Thales Alenia Space, Rapita Systems, AdaCore, AbsInt.

ALL-TIMES

Integrating European Timing-Analysis Technology

A research project within the European Commission’s 7th Framework Programme on Research, Technological Development and Demonstration. The aim was to combine available timing tools, thus strengthening the European lead in the timing-analysis area. ALL-TIMES successfully enabled interoperability of various tools from SMEs and universities, and developed integrated tool chains using open tool frameworks and interfaces.

Consortium: Mälardalen University, AbsInt, TU Vienna, Symtavision, Gliwa, Rapita Systems.

ES_PASS

Embedded Software Product-Based Assurance

A two-year project supported by the ITEA2 program (Information Technology for European Advancement). It focused on the improvement, integration, and dissemination of product-based software verification techniques.

Consortium: CS Information Systems, Airbus, AbsInt, Daimler, Esterel, Thales, CEA, Peugeot Citroën, Continental, EADS, ENS, ONERA, Fraunhofer FIRST, GTD Spain, Institut für Bahntechnik, Saarland University, TUs of Munich and Madrid.

SuReal

Safety Guarantees under Real-Time Requirements

A middle-term research project focused on the creation of a continuous development process for embedded systems that enables formal verification of safety-critical real-time aspects.

Consortium: AbsInt, DFKI, Symtavision, ScopeSET, aicas allerton, TUs of Dresden, Brunswick, and Munich.

Interest

This project significantly improved the integration and interoperability of various tools for embedded-software development, in addition to developing novel techniques for system-level and node-level analysis of nonfunctional properties such as worst-case execution timing, stack usage and schedulability. Our contribution included the integration of aiT and StackAnalyzer with SCADE, ASCET, SymTA/S, and RT-Druid.

Consortium: AbsInt, Esterel, ETAS, Symtavision, Evidence, DecomSys, Unis.

EmBounded

This project identified, quantified and certified resource-bounded code

in a domain-specific high-level programming language for real-time

embedded systems. Using formal models of resource consumption as

a basis, the project developed static analyses for time and space consumption

and assessed these against realistic applications for embedded systems.

Consortium: University of St. Andrews, Heriot-Watt University, AbsInt, Ludwig-Maximillian University, LASMEA.

Consortium: University of St. Andrews, Heriot-Watt University, AbsInt, Ludwig-Maximillian University, LASMEA.

Verisoft and Verisoft XT

This long-term research project focused on the creation of methods and tools that allow persistent formal verification of the design of integrated computer systems. Among other things, from 2007 to 2010 researchers from the Verisoft XT project partnered up with Microsoft to verify code from Hyper-V, a multi-core x64 hypervisor, using a verifier for concurrent C code.

Consortium and partners: BMW, University of Saarland, AbsInt, DFKI, Max Planck Institute for Computer Science, Audi, Infineon, Bosch, Microsoft, SYSGO, TÜV Süd, OneSpin Solutions, Universities of Bremen, Freiburg, and Koblenz, TU Kaiserslautern, TU Munich, ESG, Sirrix, and others.

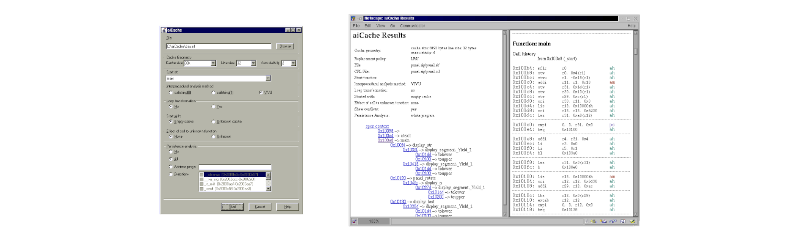

DAEDALUS

Validation of Critical Software by Static Analysis and Abstract Testing

A shared-cost research and technology development project

of the European IST Programme, focused on validation

of critical avionics software. Our contribution included creating

the first market-ready version of our flagship product aiT

for static analysis of the worst-case execution time of tasks in real-time systems.

Consortium: Airbus France, ENS, AbsInt, PolySpace Technologies,

CEA, CNRS-LIX, Universities of Copenhagen, Tel-Aviv, Saarland, and Trier.

Consortium: Airbus France, ENS, AbsInt, PolySpace Technologies,

CEA, CNRS-LIX, Universities of Copenhagen, Tel-Aviv, Saarland, and Trier.

ASTEC

Advanced Software Technology

This long-term project developed and supported industrially applicable techniques for software specification, design, and development. Particular emphasis was put on methods supporting the development of software for communication and control applications.

Consortium: Uppsala University, Mälardalen University, SICS, ABB, Ericsson, Volvo, IAR, T-Mobile UK, AbsInt, Telelogic, Arcticus, Cross Country Systems, ENEA, ESAB, Mecel, Mobile Arts, Prover Technology, TIDORUM, UPAAL, Validation, WM Data Validation, Virustech, Volcano Communication Technologies, ESAB Welding Equipment.

Project partners by country

Germany | ||

| SYSGO | AQUAS, TwinSpace, MORAL, Scale4Edge, Interested, EMPHASE, ARAMiS, ARAMiS II, Verisoft XT, TRISTAN | |

| TU Munich technical university | ASSUME, Scale4Edge, SuReal, ES_PASS, MBAT, ARAMiS II, Verisoft, Verisoft XT, TRISTAN | |

| Bosch | ASSUME, Scale4Edge, PREDATOR, EMPHYSIS, Verisoft XT, ARAMiS, ARAMiS II, TRISTAN, TIMMO-2-USE | |

| DLR, German Aerospace Center | ARGO, CESAR, QSMA, Scale4Edge, EMPHYSIS, ARAMiS II, Verisoft, Verisoft XT | |

| Symtavision until the 2016 takeover by Luxoft | ALL-TIMES, SuReal, Interest, Interested, ARAMiS, ARAMiS II, TIMMO-2-USE | |

| Infineon Technologies | CESAR, Scale4Edge, EMPHASE, Verisoft, Verisoft XT, TRISTAN | |

| Saarland University | Verisoft, Verisoft XT, artist2, DAEDALUS, PREDATOR, ES_PASS | |

| Fraunhofer Societies and Institutes incl. Fraunhofer FIRST, Fraunhofer Institute for Integrated Circuits, Fraunhofer Society for Applied Research | MBAT, ARAMiS II, CESAR, TRISTAN, ARGO, ES_PASS | |

| TU Kaiserslautern technical university | Scale4Edge, Verisoft XT, PROFORMA, ARAMiS II, FORTE, FORTISSIMO | |

| OFFIS, Oldenburg Institute for Information Technology | ASSUME, CESAR, MBAT, ARAMiS, ARAMiS II, Verisoft | |

| Siemens | CESAR, EMPHYSIS, MBAT, ARAMiS II, Interested, Scale4Edge | |

| TU Brunswick technical university | SuReal, CERTAINTY, EMPHASE, ARAMiS II, TIMMO-2-USE | |

| TU Darmstadt technical university | CONIRAS, Scale4Edge, Verisoft, Verisoft XT, TRISTAN | |

| Airbus Airbus Defense and Space, Airbus Operations | CESAR, MBAT, ARAMiS, ARAMiS II | |

| Daimler | ASSUME, ES_PASS, MBAT, ARAMiS | |

| KIT, Karlsruhe Institute of Technology | ARGO, ASSUME, ARAMiS, ARAMiS II | |

| Audi | EMPHASE, Verisoft XT, ARAMiS, ARAMiS II | |

| Accemic | CONIRAS, ARAMiS II, TRISTAN | |

| BTC Embedded Systems | ASSUME, CESAR, MBAT | |

| Continental | ARAMiS, ARAMiS II, TIMMO-2-USE | |

| DFKI, German Research Center for Artificial Intelligence | Verisoft, Verisoft XT, SuReal | |

| emmtrix Technologies | ARGO, QSMA, TwinSpace | |

| FZI, Karlsruhe Research Center for Information Technology | ASSUME, FreeSBee, Scale4Edge | |

| IHP, Leibniz Institute for High-Performance Microelectronics | MORAL, Scale4Edge, EMPHASE | |

| OneSpin Solutions | Verisoft, Verisoft XT, FORTISSIMO | |

| University of Luebeck | CONIRAS, TwinSpace, ARAMiS II | |

| aicas | SuReal, TRISTAN | |

| BMW | Verisoft, ARAMiS | |

| DENSO | EMPHASE, ARAMiS II | |

| dSPACE | EMPHYSIS, TIMMO-2-USE | |

| e:fs TechHub | TwinSpace, EMPHYSIS | |

| EPOS Embedded Core & Power Systems | Scale4Edge, TRISTAN | |

| ESG | Verisoft XT, Interested | |

| ETAS | EMPHYSIS, Interest | |

| Max Planck Institute for Computer Science | Verisoft, Verisoft XT | |

| MinRes Technologies | Scale4Edge, TRISTAN | |

| NXP | TwinSpace, TRISTAN | |

| PikeTec until the 2023 takeover by Synopsys | EMPHYSIS, MBAT | |

| University of Augsburg | TwinSpace, ARAMiS II | |

| University of Bremen | Verisoft XT, Scale4Edge | |

| University of Freiburg | Scale4Edge, Verisoft XT | |

| University of Kiel | ASSUME, ARAMiS II | |

| University of Koblenz | Verisoft, Verisoft XT | |

| University of Paderborn | Scale4Edge, TIMMO-2-USE | |

| Tensor Embedded | TwinSpace, TRISTAN | |

| TU Clausthal technical university | QSMA, TwinSpace | |

| TU Dortmund technical university | PREDATOR, artist2 | |

| TU Dresden technical university | Scale4Edge, SuReal | |

| Vector Informatik | ARAMiS, ARAMiS II | |

| Altair Engineering | Scale4Edge | |

| Ansys Medini Technologies | AQUAS | |

| cadence | EMPHASE | |

| CARIAD — Automotive Software for Volkswagen | TwinSpace | |

| CodaSip | TRISTAN | |

| Diehl Aerospace | ARAMiS II | |

| Eclipse Foundation Europe | TRISTAN | |

| edacentrum | Scale4Edge | |

| ElektroBit | ARAMiS II | |

| ESI ITI | EMPHYSIS | |

| Expleo Germany | ASSUME | |

| fortiss Research Institute of Bavaria | ARAMiS II | |

| General Electric | ARAMiS II | |

| Gliwa | ALL-TIMES | |

| Hensoldt | ARAMiS II | |

| HM, Munich University of Applied Sciences | Scale4Edge | |

| Inchron | TIMMO-2-USE | |

| Institut für Bahntechnik | ES_PASS | |

| Kasper & Oswald | FreeSBee | |

| KSB | ARAMiS II | |

| Lauterbach | Scale4Edge | |

| Liebherr Aerospace | ARAMiS II | |

| LMU, Ludwig Maximilian University of Munich | EmBounded | |

| MBtech Group | MBAT | |

| Microsoft | Verisoft XT | |

| Model Engineering Solutions | ASSUME | |

| OpenSynergy | ARAMiS II | |

| RheinMain University of Applied Sciences | AQUAS | |

| RWTH Aachen university | artist2 | |

| Schaeffler | ARAMiS II | |

| ScopeSET | SuReal | |

| Silexica | ARAMiS II | |

| Silicon Radar | EMPHASE | |

| Sirrix | Verisoft XT | |

| T-Systems International | Verisoft | |

| Thales Transport Solutions Deutschland | ES_PASS | |

| Timing Architects | ARAMiS II | |

| TU Hamburg-Harburg technical university | TeamPlay | |

| TÜV Süd | Verisoft XT | |

| University of Cottbus-Senftenberg | TwinSpace | |

| University of Trier | DAEDALUS | |

| University of Tuebingen | Scale4Edge | |

| Validas | QSMA | |

| Verified Systems International | PROFORMA | |

| WIKA Mobile Control | ARAMiS II | |

France | ||

| CEA, Commission for Atomic Energy and Alternative Energies | AQUAS, CESAR, DAEDALUS, Interested, ES_PASS, MBAT, EMPHYSIS, TRISTAN | |

| Thales incl. Thales AVS, Thales Alenia Space France, Thales Six GTS, Thales Global Services, Thales DIS Design Services | AQUAS, ASSUME, CESAR, Interested, ES_PASS, MBAT, CERTAINTY, TRISTAN | |

| Airbus Airbus Operations, Airbus Defence & Space, EADS Airbus | ASSUME, CESAR, Interested, ES_PASS, MBAT, DAEDALUS, PREDATOR | |

| Esterel Technologies | ASSUME, CESAR, Interest, Interested, ES_PASS | |

| ENS | ASSUME, DAEDALUS, ES_PASS, MBAT | |

| INRIA INRIA Rennes, INRIA Sophia Antipolis | ASSUME, CESAR, TeamPlay, TIMMO-2-USE | |

| Dassault | CESAR, MBAT, EMPHYSIS | |

| Delphi | CESAR, TIMMO-2-USE | |

| Kalray | ASSUME, CERTAINTY | |

| ONERA, National Office of Aerospace Studies and Research | ES_PASS, CESAR | |

| Safran Safran Aircraft Engines (Snecma), Safran Electronics & Defense (Sagem), Safran Helicopter Engines, Safran Landing Systems | ASSUME, CESAR | |

| Siemens Industry Software | AQUAS, EMPHYSIS | |

| ST Microelectronics | TRISTAN, artist2 | |

| All4tec, Alliance pour les Technologies de l’Informatique | MBAT, AQUAS | |

| AdaCore | COLA | |

| Alstom Transport | MBAT | |

| ARTTIC | CERTAINTY | |

| Clearsy | AQUAS | |

| CNRS, National Center for Scientific Research | CESAR | |

| Continental Automotive France | ES_PASS | |

| CS Systèmes d’Information | ES_PASS | |

| EADS EADS Astrium, EADS Innovation Works | ES_PASS | |

| FH Electronics | EMPHYSIS | |

| Greenwaves Technologies | TRISTAN | |

| Institut Mines-Telecom, Telecom ParisTech | AQUAS | |

| Institut National Polytechnique de Toulouse | ES_PASS | |

| Institut National Polytechnique de Grenoble | EMPHYSIS | |

| LASMEA, Blaise Pascal University, Clermont-Ferrand | EmBounded | |

| Magillem Design Services | AQUAS | |

| NXP Semiconductors France | TRISTAN | |

| OSE Engineering | EMPHYSIS | |

| Peugeot Citroën Automobiles | ES_PASS | |

| PolySpace Technologies | DAEDALUS | |

| RealTime-at-Work | TIMMO-2-USE | |

| Renault | EMPHYSIS | |

| Robert Bosch France | TRISTAN | |

| Scilab Enterprises, Dassault Systèmes | ARGO | |

| Soben | EMPHYSIS | |

| Joseph Fourier University | CERTAINTY | |

| University of Rennes 1 | ARGO | |

| University of Sorbonne | ASSUME | |

Sweden | ||

| Mälardalen University | ALL-TIMES, ASSUME, ASTEC, artist2, MBAT, TIMMO-2-USE | |

| Volvo incl. Volvo Technology, Volvo Teknisk Utveckling, Volvo Personvagnar | CESAR, MBAT, ASTEC, EMPHYSIS, TIMMO-2-USE | |

| KTH, Royal Institute of Technology | ASSUME, CESAR, MBAT | |

| Arcticus Systems | ASSUME, ASTEC, TIMMO-2-USE | |

| Uppsala University | ASTEC, CERTAINTY | |

| RISE SICS, Swedish Institute of Computer Science | EMPHYSIS, ASTEC | |

| ENEA | ASTEC, MBAT | |

| Linköping University | EMPHYSIS | |

| Scania | ASSUME | |

| Hitachi Energy | CESAR | |

| ABB Automation Technologies | ASTEC | |

| Alten | MBAT | |

| Autoliv | EMPHYSIS | |

| Chalmers University of Technology | TIMMO-2-USE | |

| Cross Country Systems | ASTEC | |

| Dassault Systems Sweden | EMPHYSIS | |

| Ericsson | ASTEC | |

| ESAB Welding Equipment | ASTEC | |

| FindOut Technologies | ASSUME | |

| IAR Systems | ASTEC | |

| IBM Svenska | MBAT | |

| Mecel | ASTEC | |

| Mobile Arts | ASTEC | |

| Modelon | EMPHYSIS | |

| Prover Technology | ASTEC | |

| Telelogic | ASTEC | |

| TIDORUM | ASTEC | |

| Time Critical Networks | TIMMO-2-USE | |

| UPAAL | ASTEC | |

| Validation | ASTEC | |

| WM Data Validation | ASTEC | |

| VINNOVA, Swedish government agency for R&D | ASTEC | |

| Virtutech | ASTEC | |

| Volcano Communication Technologies | ASTEC | |

Italy | ||

| Università di Bologna | CESAR, PREDATOR, TRISTAN | |

| Selex Sistemi Integrati | CESAR, MBAT | |

| Intecs Solutions | AQUAS, T-CREST | |

| Evidence | Interest, Interested | |

| Leonardo | MBAT, TRISTAN | |

| Alenia Aermacchi merged into Leonardo in 2016 | MBAT, CESAR | |

| Università degli studi dell’Aquila | AQUAS | |

| Hitachi Rail | CESAR | |

| Centro Ricerche FIAT | CESAR | |

| Danieli Automation | CESAR | |

| Università degli studi di Trieste | CESAR | |

| RedCat Devices | MORAL | |

| Magneti Marelli | Interested | |

| Scuola Superiore Sant’Anna | PREDATOR | |

| ALES | MBAT | |

| AMET | MBAT | |

| Ansaldo | MBAT | |

| ST Microelectronics | TRISTAN | |

| E 4 Computer Engineering | TRISTAN | |

| Politecnico di Torino | TRISTAN | |

| University of Padua | COLA | |

United Kingdom | ||

| Rapita Systems | ALL-TIMES, TIMMO-2-USE, COLA | |

| University of St. Andrews | EmBounded, TeamPlay | |

| University of York | artist2, T-CREST | |

| Airbus UK | MBAT, CESAR | |

| Atego Systems | Interested | |

| Auvation Software | CESAR | |

| Quintec Associates | CESAR | |

| Ricardo UK | MBAT | |

| T-Mobile UK | ASTEC | |

| University of Bristol | TeamPlay | |

| Heriot-Watt University | EmBounded | |

| City, University of London | AQUAS | |

| University of Manchester | CESAR | |

| The Chancellor, Masters and Scholars of the University of Oxford | CESAR | |

The Netherlands | ||

| TU/e, Eindhoven University of Technology | ASSUME, T-CREST | |

| University of Twente | ASSUME, TRISTAN | |

| University of Amsterdam | TeamPlay | |

| NLR, Netherlands Aerospace Center | TRISTAN | |

| NXP Semiconductors Netherlands | ASSUME | |

| Irdeto | TRISTAN | |

| Recore Systems | ASSUME | |

| Technolution | TRISTAN | |

| TNO | ASSUME | |

| VDL Enabling Transport Solutions | ASSUME | |

| Verum Software Tools | ASSUME | |

Austria | ||

| Vienna University of Technology | ALL-TIMES, T-CREST, artist2 | |

| AIT Austrian Institute of Technology | AQUAS, MBAT | |

| AVL List | CESAR, MBAT | |

| Infineon Technologies Austria | CESAR, MBAT | |

| Virtual Vehicle Research | CESAR, MBAT | |

| Siemens Austria | AQUAS, TRISTAN | |

| TU Graz technical university | MBAT, TRISTAN | |

| Decomsys (now ElektroBit) | Interest | |

| TTTech Computertechnik | Interested | |

| NXP Semiconductors Austria | TRISTAN | |

| Strohmayer Klaus | TRISTAN | |

Spain | ||

| Thales Alenia Space | AQUAS, MORAL, COLA, TeamPlay | |

| Tecnalia Research & Innovation | AQUAS, CESAR | |

| Acciona Construccion | CESAR | |

| GTD | ES_PASS | |

| Instituto Tecnológico de Informática | AQUAS | |

| Intergrasys | AQUAS | |

| RGB Medical Devices | AQUAS | |

| TU Madrid technical university | ES_PASS | |

Greece | ||

| Aristotle University of Thessaloniki | CESAR | |

| Hellenic Aerospace Industry | CESAR | |

| Irida Labs | TeamPlay | |

| National Technical University of Athens | CESAR | |

| Technological Educational Institute of Western Greece | ARGO | |

| Athina-Erevnitiko Kentro Kainotomias stis Technologies tis Pliroforias, ton Epikoinonion kai tis Gnosis | CESAR | |

Turkey | ||

| Arçelik | ASSUME | |

| Ericsson Ar-Ge | ASSUME | |

| Ford Otosan | ASSUME | |

| Havelsan | ASSUME | |

| KoçSistem Information and Communication Services | ASSUME | |

| UNIT Information Technologies R&D | ASSUME | |

| Yongatec Microelectronics | TRISTAN | |

Denmark | ||

| University of Copenhagen | DAEDALUS | |

| University of Southern Denmark | TeamPlay | |

| Sky-Watch | TeamPlay | |

| Aalborg University | MBAT | |

| Danmarks Tekniske Universitet, Lyngby | T-CREST | |

Belgium | ||

| Dana Belgium | EMPHYSIS | |

| Siemens Industry Software | EMPHYSIS | |

| University of Antwerp | EMPHYSIS | |

| The Open Group | T-CREST | |

| IMEC, Interuniversity Microelectronics Center | TRISTAN | |

Finland | ||

| Cargotec | TRISTAN | |

| VLSI Solution | TRISTAN | |

| Nokia Solutions and Networks | TRISTAN | |

| Tampereen Korkeakoulusaatio | TRISTAN | |

Norway | ||

| ABB | CESAR | |

| NTNU, Norwegian University of Science and Technology | CESAR | |

| SINTEF, Independent Organisation for Applied Research, Technology and Innovation | CESAR | |

Czech Republic | ||

| UNIS | Interest, Interested | |

| Brno University of Technology | AQUAS | |

| TrustPort | AQUAS | |

Portugal | ||

| Critical Software | CESAR | |

| GMV | T-CREST | |

Israel | ||

| Tel-Aviv University | DAEDALUS | |

| Siemens Electronic Design Automation Israel | TRISTAN | |

Switzerland | ||

| Swiss Federal Institute of Technology, ETH Zurich | PREDATOR, CERTAINTY, TRISTAN | |

| Synthara | TRISTAN | |

Estonia | ||

| Elvior OÜ | MBAT | |

Canada | ||

| Maplesoft | EMPHYSIS | |

Poland | ||

| Antmicro | TRISTAN | |

Romania | ||

| NXP Semiconductors Romania | TRISTAN | |