Improved path replacements |

Improved Results Viewer |

MPC55xx: support for TLB |

Targets

a³ for C16x now supports CX167CI-32F40F.

Installation/deinstallation

Prior to installation or deinstallation, the installer now detects running processes of the tool in question and asks the user to close them so as to avoid problems.

Qualification Support Kits (QSKs)

- Added qualification support for a³ for C16x (XC167CI-32 derivative) in combination with the TASKING compiler v8.6r2.

- Replaced bash-based evaluation test runs by QtScript files

that are interpreted by

qualifygui. - Added a progress bar to

qualifyguito show the percentage of finished test cases. - Replaced/removed placeholders in reports. The idea is that the documents should not be edited by the customer anymore. Much rather, they are now stand-alone reports documenting that the tools work within the AbsInt test environment. “AbsInt test environment” means that AbsInt has developed custom test cases for the different requirements.

- MPC755/PPC750: removed the test case

qk_apx_delay_all_mastersas this option has been removed. - H8: removed the test case

qk_apx_assume_data_accessesas this option does not exist in the GUI for the H8.

XTC Handling

Extended the specification to allow more a³ specific options to be passed over.

GUI

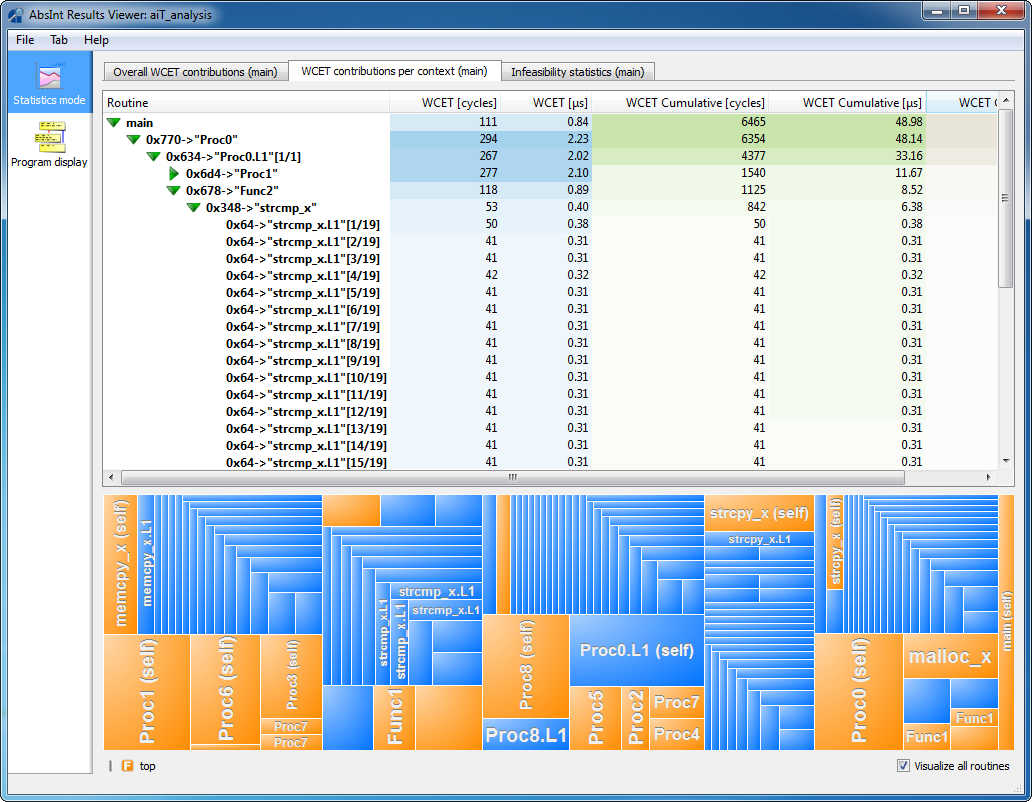

- Introduced the Results Viewer for the Stack/Value/aiT/TimingExplorer analyses.

The Results Viewer provides the stack and WCET contribution tables. In addition, there are:

- A context sensitive WCET contribution table and chart.

- A table providing statistics about infeasible routines/blocks/instructions. This infeasibility report is also available in the textual and XML reports.

- Stack analysis now supports specifying an expected result, which is then checked against the result computed by the analysis.

- Better import and conversion of obsolete/changed APX options from previous releases. Quiet conversion if possible, else inform user.

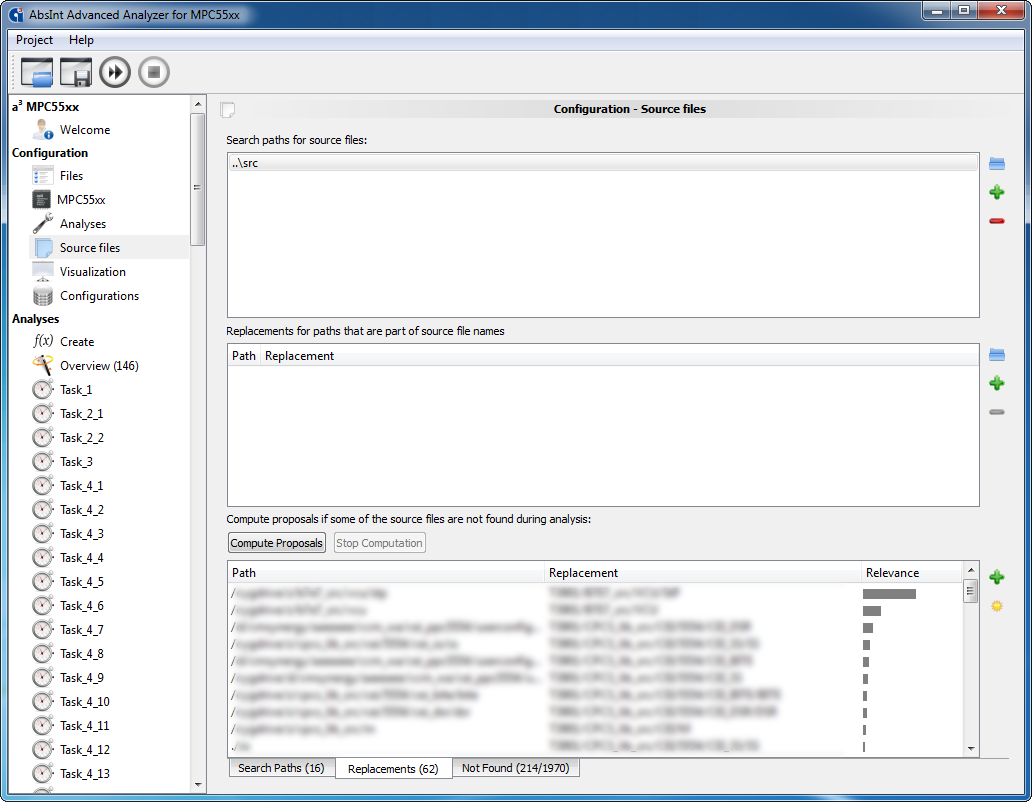

- Improved path replacement algorithm. Proposed path replacements are now weighted according to their estimated relevance.

- Improved navigation between error messages and the corresponding instruction in the call graph.

- The Variables and the Functions view now allow a contiguous selection of table entries.

- Generally improved the loading speed of APX projects.

- More robust import and export of machine-settings files.

- Analyses view → Reporting tab: New slider “Pedantic level” to control the effects of warnings and non-fatal errors. Allows the user to enforce analysis termination even for normal errors or warnings.

- Interactive Value Analysis: Contexts for interactive value analysis can be selected by name via Ctrl+G in the interactive value analysis view.

- Stack/Value/aiT Analysis:

- Better visualisation of routines and blocks that are infeasible because of backwards propagation. They are shown in lightgray in the graph.

- Removed the option to disable the backwards propagation of infeasibilities.

- Changed the name and semantics for the visualisation option “Display infeasible routines”. It is now called “Display all infeasible routines” as the first level of infeasible routines is always shown to make it easier to spot problems.

- SCADE Integration: only test for Flexnet tokens on GUI start, not take them.

- Autoscrolling in message view is re-enabled if the user scrolls to bottom, even if errors/warning occured.

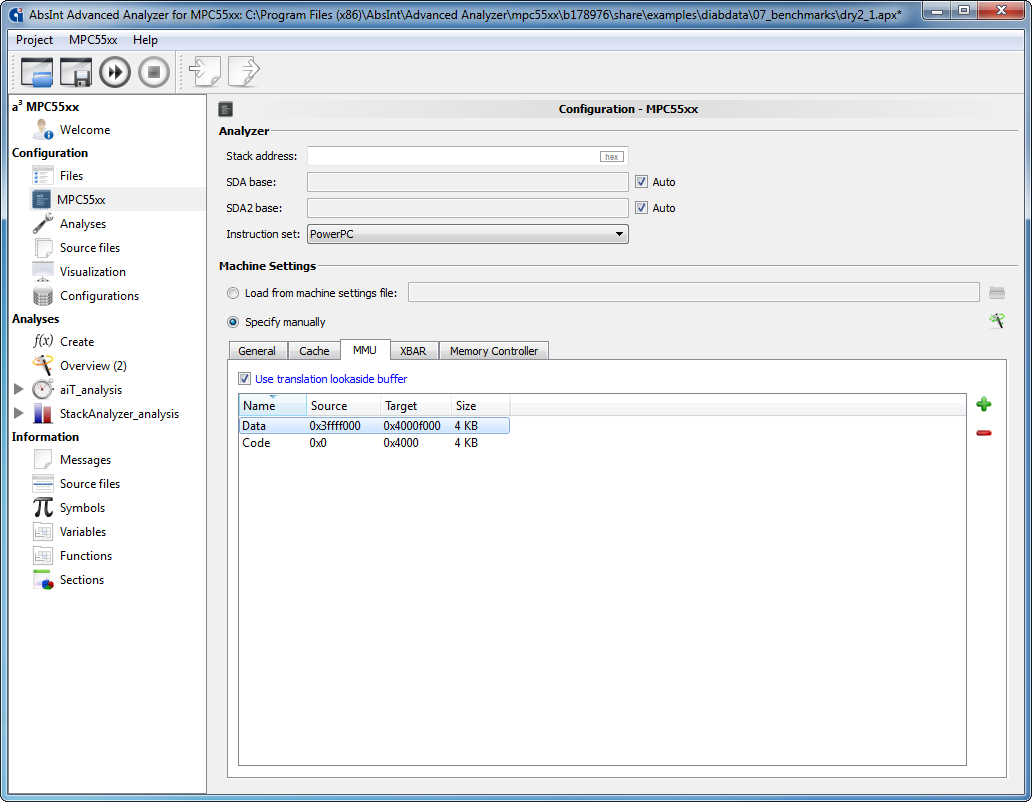

- MPC55xx: added support for the translation lookaside buffer (TLB).

AIS

- Removed the following functors from the numeric expressions:

bounded (...)exact (...)high (...)low (...)try (...)value ()

- Changed the semantics of the following functors:

restrict (a, b, ...)now leads to an error if the intersection is emptyrange (a, b)anda..bnow leads to an error if the range is emptyE with x % a == bnow leads to an error if the result is emptyswitch (...)now leads to an error if no switch case matches

- Allowed

default-unrollto be larger thanmax-unrollin the mapping specification. - Inform user if a null pointer is found in the function-pointer array but there is no “null” option in the annotations to ignore such entries.

- When a

callsorcalls viaannotation introduces an external routine, as the target is not contained in the executable, a corresponding message is issued that includes references to the problematic annotations. - The execution time of a not-analyzed target of a computed call may now be an expression rather than only a constant.

Decoding

- Better handling of "NOBITS" ELF sections. They are only used as a fallback if no other section is matching for the address region, as they contain no data.

- Improved decoding loop (

exec2crland value analysis cooperation). - XML Report: Output which routines are loop routines and which type of loops they are (begin/end/unknown).

- When automatically resolving computed branches or calls, the decoder now informs the user about register contents being used to resolve the branch or call respectively.

- Better selection of routine names if multiple names are possible (e.g. code labels have lower priority than real function names).

- Better handling of debug line information.

- The report file now contains the location of the user annotations that were used to resolve computed branch or call targets.

- ARM/HC11/HCS12:

- Support for the Keil MDK-ARM compiler suite.

- Decoding allows duplicated code to e.g. inline again tail optimized routine ends.

- SPARC:

- Improved SPARC switch table decoding patterns that are now able to cope with compiler optimizations such as annulled conditional branches.

- Improved annotations with respect to delay slots.

- TriCore:

- For the TASKING compiler, contents of the ROM Section “[EXAMPLE]” will now be automatically copied to the relocated RAM Section “EXAMPLE”.

- For the TASKING compiler, routine symbols will be created for a routine with the shortened section name of this routine if no real symbol was found in the symbol table.

- Improved decoder patterns that are now able to automatically resolve even more computed branches (switch tables) and calls (via function pointer arrays).

- Extended TriCore decoder to use iterative decoding.

- V850: general improvements to the decoder. Better recognition of computed branches and calls.

Value analysis

- Improved loop and value analysis precision and performance.

- Removed difference bound matrices.

- If a loop is marked as infeasible handle it is now handled like an unreached loop and skipped in the loop analysis. This avoids loop bound contradiction warnings for infeasible loops.

- Added detection of simple busy waiting loops that warns if the memory cell on which the loop waits is not annotated as volatile.

Instead of calculating with only one interval of values the user can specify to use a set of intervals for each register/memory cell. To use more than one interval per register/memory cell the option “Analyses” → “Advanced” → “Size limit for interval sets” has to be increased to more than 1. Alternatively, the user can add an annotation of the form:

routine "foo" features "size_limit_for_interval_sets" = N

This increases the number of intervals per register/memory cell in the specified routine to N independently of the global setting.

- Extended feasability analysis now propagates infeasible through external routines that are annotated to always return.

- SPARC: improved infeasible control flow transition of branch and call instructions.

Cache and pipeline analysis

- Improved cache persistence analysis precision.

- Improved cache persistence combined with local WCET analysis mode.

- C16x: added support for the return stack in the C166Sv2 microarchitecture analysis.

- ERC32: improved precision of ERC32 pipeline model.

- LEON2: refined analysis model with respect to instruction cache behavior and uncached code fetches.

- MPC55xx/MPC56xx: improved memory region sanity checks.

- MPC7448:

- Improved handling of speculative write accesses.

- Memory controller model does not accept the PCI memory type “generic” anymore. Instead the device-specific types “PCI_AFDX” or “PCI_COREIO” have to be used in area annotations.

- Implemented trace-based observed

eieiobehavior instead of the documented one. - In contrast to documentation, synchronized the bus access queue with the MPX bus clock which explains observed NVSRAM traces.

- Removed “PCI Bridge IP Wait States” GUI options after switching to a new PCI controller model.

- MPC7448s:

- Improved handling of speculative write accesses.

- In contrast to documentation, synchronized the bus access queue with the MPX bus clock.

- Implemented trace-based observed

eieiobehavior instead of documented one.

- TriCore: improved analysis performance.

- V850: improved analysis precision.

Visualization and reporting

- Correct handling of TLB analysis additional cycles in the XML report file.

- Clock rate information is now included in the XML report.

- The textual report now contains the contexts per routines and additionally infeasibility statistics.

- Routines that are inside a strongly-connected-component (SCC) are no longer colored differently if they are infeasible.

- Fixed “Goto source” in result graph.