New targets

- All tools for AURIX now support 2nd-gen TC33x, TC35x, and TC36x.

- All tools for MIPS now support the microMIPS32 ISA version 3 and 5, as well as the MIPS DSP Module for MIPS32.

AbsInt License Manager

The ALM now allows specifying a log file and log size. All connections to the server are then logged to the file in the JSON line format. After the specified log size is exceeded, the log file is rotated.

--log-file <file>creates the log file, otherwise no log file is created--max-log-file-size <size>specifies the maximum log size in MB

Qualification Support Kits

- New QSKs:

- aiT for ARM/THUMB with ti-20.2.1.lts

- StackAnalyzer for ARM/THUMB with ti-20.2.1.lts

- StackAnalyzer for ARM/ARM with ti-20.2.1.lts

- StackAnalyzer for MIPS

- TimeWeaver for PPC

- TimeWeaver for ARM/AArch64

- Improvements:

- Unified QSK ZIP file names to be uniform to the corresponding product ZIP file names.

qk_ais2_area_properties_contentnow triggers a #3088 warning about conflict for memory writes to constant areas.qk_ais2_stack_single_heightnow triggers a contradiction message between computed and annotated stack height.qk_ais2_not_analyzed_code_timenow checks for zero-cycle contributions.qk_ais2_count_memory_accessesnow covers accesses to areas distributed across different basic blocks.qk_setting_area_properties_locked(board-specific test case for board tms570lc4357_arm) now covers code locking.qk_ais2_attribute_predefined(_(tc1797|tc377))now covers the immutable attribute<tt>core_id.- Enhanced AIS2 program point offset test cases that deal with

instruction class-relative displacements by tool runs

that cover an offset value of

0.

- New test cases:

qk_ais2_stack_alignment ARM, C16x, dsPIC, M68020, MIPS, PPC, TriCore, V850, x86 qk_ais2_allow_decoder_to_read_from_writable_memory ARM (instruction-set: arm, feature: wcet) qk_setting_calling_conventions,

qk_setting_constant_register_conflict,

qk_setting_non_factorized_return,

qk_setting_report_file,

qk_setting_unresolved_computed_branch,

qk_setting_unsupported_instruction

qk_ais2_program_point_base_interrupt_entry

qk_ais2_program_point_base_trap_entry

qk_setting_biv

qk_setting_core_idTriCore

GUI

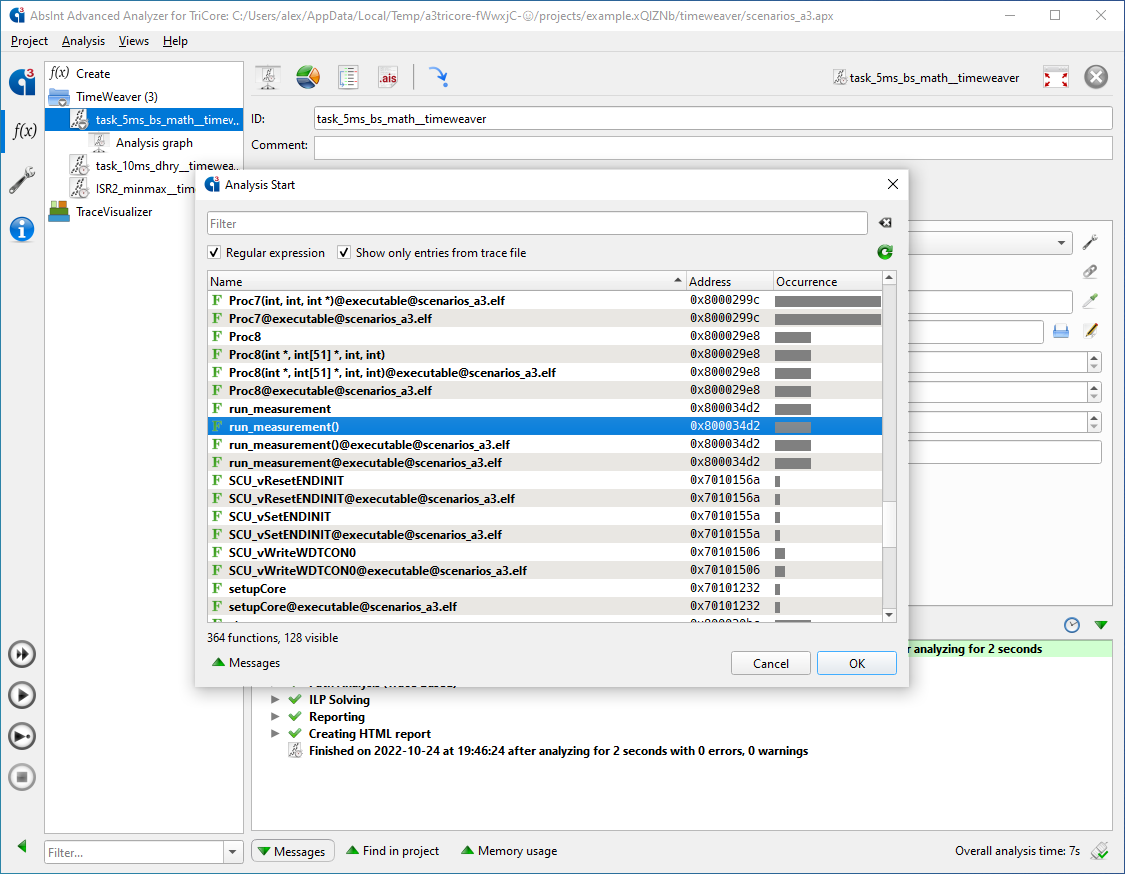

- The analysis start picker now shows the trace occurrences according to the entries in the provided trace files.

- The configuration that is associated with the currently active analysis can now be easily edited using the configuration tool button.

- The GUI now properly restores analysis comments.

- Improved interactive help in AIS2 editor.

- The GUI no longer modifies the include path when creating a support archive.

- In support archives, the current analysis state can now be included as a workspace.

Visualization and results

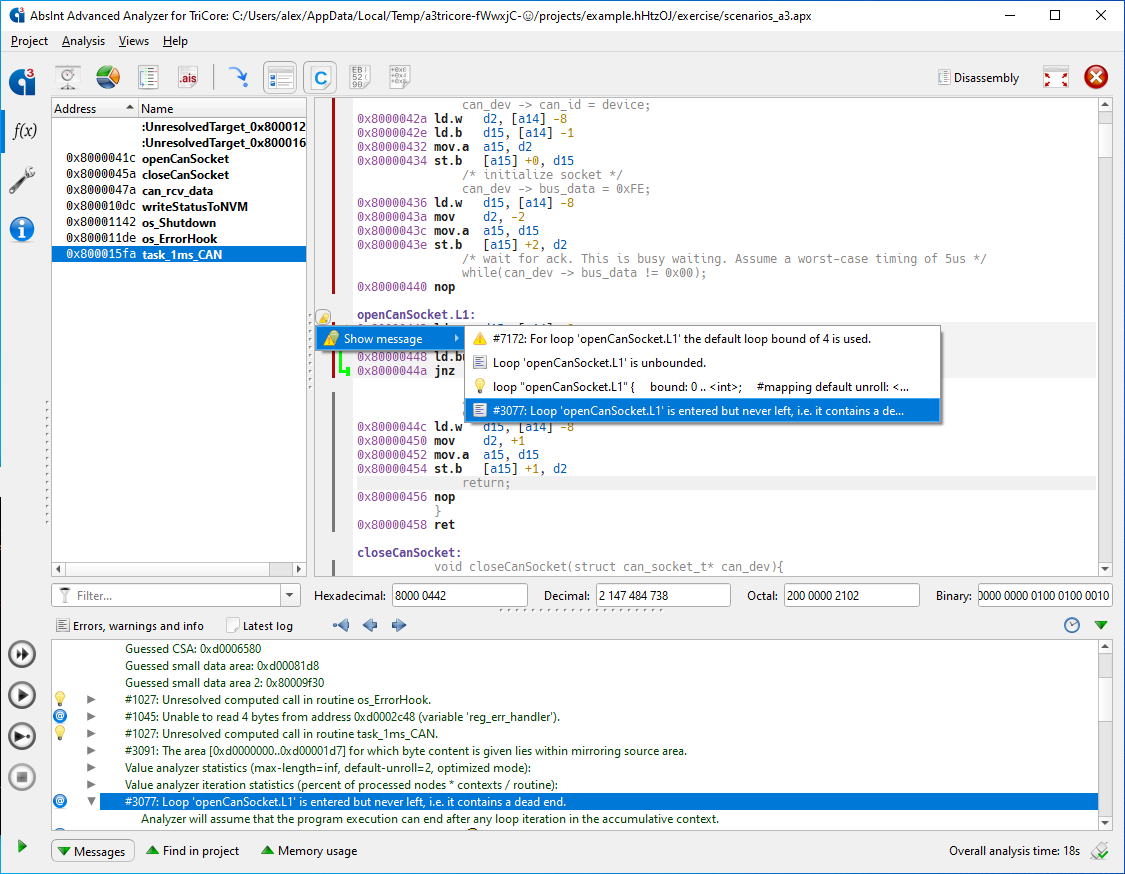

- Disassembly view now shows associated message markers.

- Improved speed and accessibility of analysis result graph info nodes.

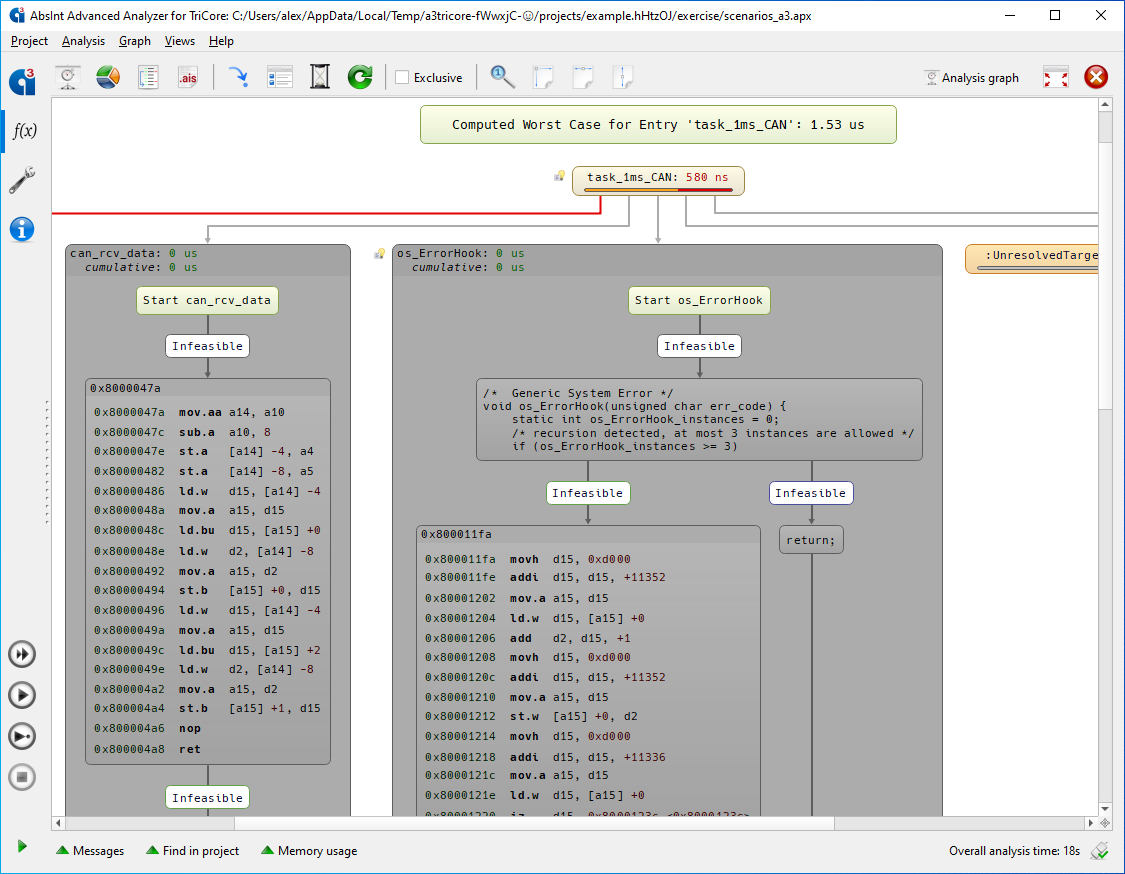

- Improved visualization of infeasible call edges in the call graph.

Reporting

Trace analysis and trace-based path analysis now print their statistics to the XML report. Example:

<trace_import_statistics>

<snippets total="16" starts="16" ends="16" />

<events total="7392" />

<lines total="86534" used="85726" />

</trace_import_statistics>

<trace_path_statistics min_costs="257772" max_costs="259494">

<snippets total="16" used="16" skipped="0" segments="93">

<end total="16" routine="d1_r136" />

</snippets>

</trace_path_statistics>

TimeWeaver

New option to check for contradictions in the WCET path. See user manual for details.

Annotations

- In addition to normal user registers that are propagated throughout the whole control-flow graph, it is now possible to use routine-local user registers whose lifetime is restricted to the routine they are declared at. See the user manual for further details.

- Introducing local partitioning contexts that only stay alive within the routine

they are created in.

instruction 0x1234 { begin local partitioning: .... } - Improved handling of the annotation “

instruction <pp> calls”for architectures with delay slots. - TriCore: The selected core is available in AIS2 as

attribute("core_id"); - Added ability to check whether an attribute is defined,

and to specify a default value for an attribute that is taken if it is not defined.

routine "ISR2_minmax" { assert enter with: # immutable attributes might be symbols defined(attribute("target_type")) == true, attribute("target_type") == "tc275", # immutable attributes might be numbers defined(attribute("core_id")), attribute("core_id") == 1, # immutable attributes might be not defined at all defined(attribute("foobar")) == false, # but we can specify a default value attribute("foobar", 42) == 42; }

Decoding

- The decoder guesses the stack pointer to be the last possible address in the specified stack area if no stack pointer has been provided.

- Improved handling of routines that violate the calling conventions.

- Improved speed of decoder patterns.

- Support for version 1.8 of the TriCore instruction set.

Value analysis

- Improved analysis performance for:

- larger set size limits

- routines with an excessive number of call sites

- architectures with sub-registers

- Improved handling of imprecise memory accesses.

- Improved diagnostics for invalid stack area specifications.

isa-riscv: Error #3181: The initial value 0x100000 of the register 'sp' contradicts the annotated register range [0x00000000..0x000fffff]. The analyzer will ignore the annotated range.

- Improved handling of certain rare operations in the stack analysis domain.

- Improved sharpening with the help of relational information.

- Improved DWARF heuristics to sharpen base register for accesses in more cases.

DWARF

- Improved handling of DWARF debug information in the presence of link time optimizations.

- Improved support for DWARFv5.

- Improved handling of flexible array members.

- Improved reading of template value parameters.

- Improved reading of enumerator types.

- Improved error handling of DWARF reading.

- Improved stability of DWARF debug line information reader.

ARM

- Improved precision for AArch64

LSL,LSR,ASR. - Improved branch splitting precision.

- Clarified analysis restrictions concerning mode switches

and added a corresponding warning:

isa-arm: Warning #3131: In "foo.asm", line 41:

In routine '_foo_subroutine', at address arm::0x56fc:

Instruction cps may perform a mode switch. This is not supported.

Using nop semantics instead. - Improved automatic decoding of computed control-flow transitions for Clang.

- Improved automatic switch-table decoding for the TI 20.2.1 LTS compiler.

TriCore/AURIX

- Support for version 1.8 of the TriCore instruction set

except for the hypervisor instructions

(

hvcall/rfh/cachea.*.vm/cachei.*.vm). - The instructions

CALL/CALLA/CALLIperform a read access to determine the new value of register FCX. This read access is now modeled in the decoder and the value analysis. This change can affect AIS2 annotations that use “-> read(n)” or “-> access(n)” to locate a program point if they span over a call instruction. - Improved handling of mixed calling conventions

(

call/retandfcall/fret) in the stack analysis domain. - Improved handling of writes to registers with subregisters.

- When a core has been selected in the Hardware View of the GUI,

then the corresponding value of register “

core_id” is made available to the value analysis. - The StackAnalyzer–SCADE coupling is now also available for AURIX.

V850/RH850

- The control-flow reconstruction now emits one virtual trap routine per trap class instead of one generic trap routine.

- Assuming calling conventions for both EI- and FE-level traps.

Cache and pipeline analysis

Improved handling of 64-bit addresses in generic TimingProfiler.

TimeWeaver

- Support for Lauterbach Trace32 BRANCHFLOW export trace format, which results in smaller export trace files and faster analysis. BRANCHFLOW export traces as required by TimeWeaver are generated by all Trace32 builds 151558 or higher.

- Improved memory consumption and analysis performance.

- Improved performance of path analysis and ILP solving.

- Improved handling of trace snippet ends in general, and in particular of snippets that end in the middle of the program.

- Improved call stack handling.

- Improved handling of task switches.

- Improved opcode check.

- Improved heuristics to handle return from interrupts when thread or process identifiers are unknown.

- Improve handling of TRACE ENABLE messages in Lauterbach ASCII export traces.

- Improved handling of back-to-back interrupt events (Lauterbach ASCII and FLOW export trace formats).