New targets

- aiT for ARM now supports STM32F103xx (Cortex-M3).

- TimeWeaver is now available for V850/RH850.

- StackAnalyzer and TimingProfiler for C28x now offer generic TMS320F28x as a target.

- All tools for M68k now support the Microtec C compiler.

AbsInt License Manager (ALM)

All network connections between the ALM server and its clients are now TLS-encrypted.

Upgrading your client to this release requires upgrading your ALM as well.

Old client versions will continue to work with the new ALM using the non-encrypted

legacy protocol, unless you block the corresponding port in your firewall. The default

port for the legacy protocol is 42424,

while for the new TLS connection it’s 42426.

A new environment variable AI_LICENSE_TLS is used to configure

the license, while old versions use AI_LICENSE. This enables you

to set up old and new versions to run in parallel, for example:

AI_LICENSE = alm-server@42424 AI_LICENSE_TLS = alm-server@42426

The ALM web interface is now served via HTTPS in addition to HTTP. The default

ports are 42427 and 42425, respectively.

alauncher

- The tool launcher now supports scanning for installed products in arbitrary directories

specified via the option

--dir <path> - The launcher will now auto-discover all a³ tools located in sibling

a3*directories. This enables you to unpack the product ZIP files in a directory and use the launcher of any of them to access all of them. For example, if you have a directory witha3_arm_123,a3_arm_456, anda3_c_789, you can now use the launcher ina3_c_789/binto access all three tools.

Linux support

Starting with this release, the Linux version offers native support for the Wayland windowing system.

APX

The XSD schema for APX files now allows the attribute base_address

for the tag <executable/>.

Qualification Support Kits

- New packages:

- QSK for StackAnalyzer for ARM (AArch64) with GHS 2020.1.4.

- QSK for StackAnalyzer for TriCore (32-bit) with Tasking VX 6.2r2p3.

- QSK for aiT for e200 (32-bit) with GHS 2012.1.

- Generic QSK for StackAnalyzer for C28x.

- QSK for StackAnalyzer for C28x with TI 18.2.3.lts.

- The TOR now include a general requirements section, requirements for message output functionality, and a section about input files and formats.

- Added syntax variant description

point <ProgramPoint>to the TOR ofqk_ais2_flow_constraints. - Synchronized TOR requirement

qk_ais2_program_point_offsetwith the user manual regarding the description of instruction classes. - New test cases:

qk_setting_unresolved_computed_branch all architectures qk_setting_dynamic_linking_option

qk_setting_dynamic_linking_executablesARM, PowerPC, x86 qk_setting_trace_coverage

qk_setting_trace_skipped_snippetall TimeWeavers qk_setting_relocation_type_r_aarch64_abs64

qk_setting_relocation_type_r_aarch64_copy

qk_setting_relocation_type_r_aarch64_glob_dat

qk_setting_relocation_type_r_aarch64_jump_slot

qk_setting_relocation_type_r_aarch64_relativeARM AArch64 qk_setting_relocation_type_r_ppc_addr32

qk_setting_relocation_type_r_ppc_copy

qk_setting_relocation_type_r_ppc_jmp_slot

qk_setting_relocation_type_r_ppc_relative32-bit PowerPC qk_setting_relocation_type_r_386_32

qk_setting_relocation_type_r_386_copy

qk_setting_relocation_type_r_386_glob_dat

qk_setting_relocation_type_r_386_jmp_slot32-bit x86 - The test case

qk_ais2_area_definitions_simplehas been extended to cover all variants of the functortype(). - The test case

qk_ais2_symbolic_names_labelhas been extended to cover label name construction by string expressions. - The test case

qk_setting_use_only_safe_patternshas been updated to trigger a decoder pattern marked as unsafe.

GUI

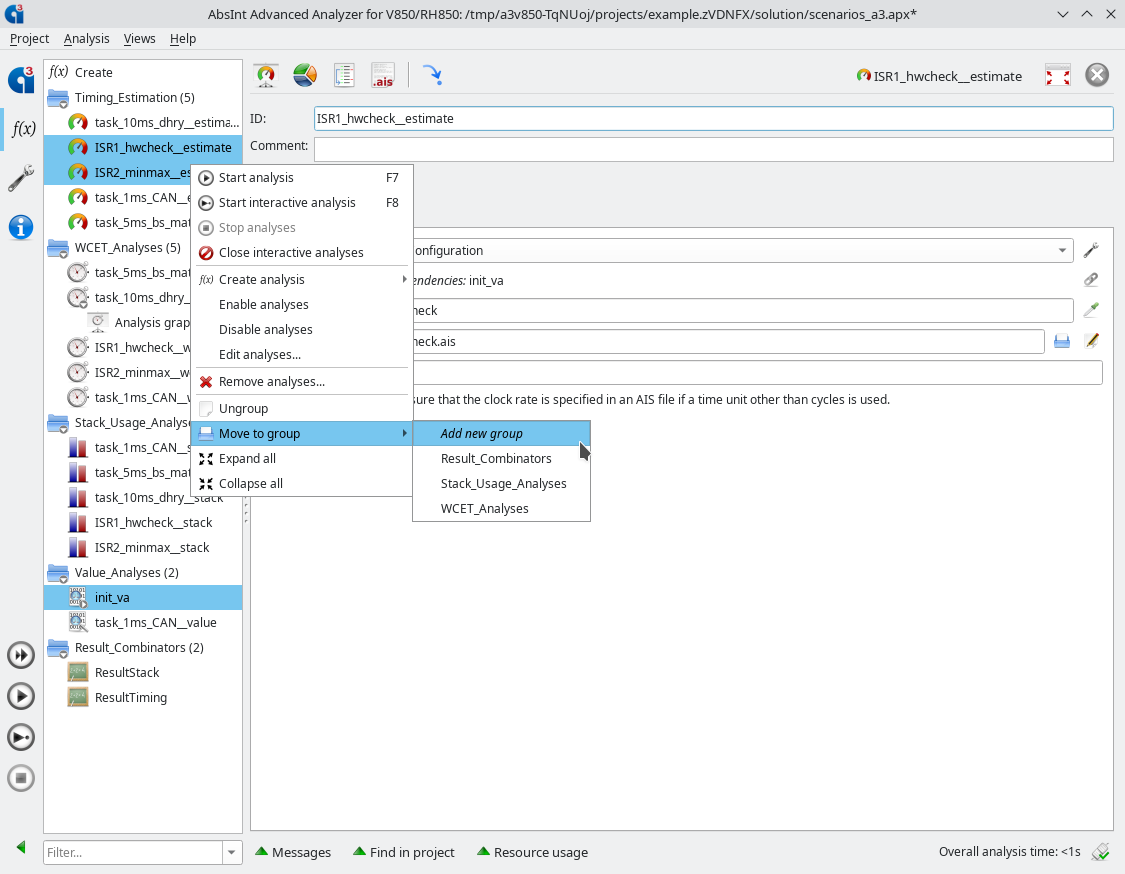

- Analysis items can now be moved to new groups.

- Analysis items can be created for a selected group.

- Improved handling of analysis dependencies, analysis groups, and dependencies to failed analyses.

- Improved visualization of syntax errors in AIS editor views.

- Improved comparison of projects with failed tool runs.

- Expected ResultCombinator results can now be modified in the analysis mass edit dialog.

- Table columns are now exported to CSV in the same order as they appear in the GUI.

Visualization and results

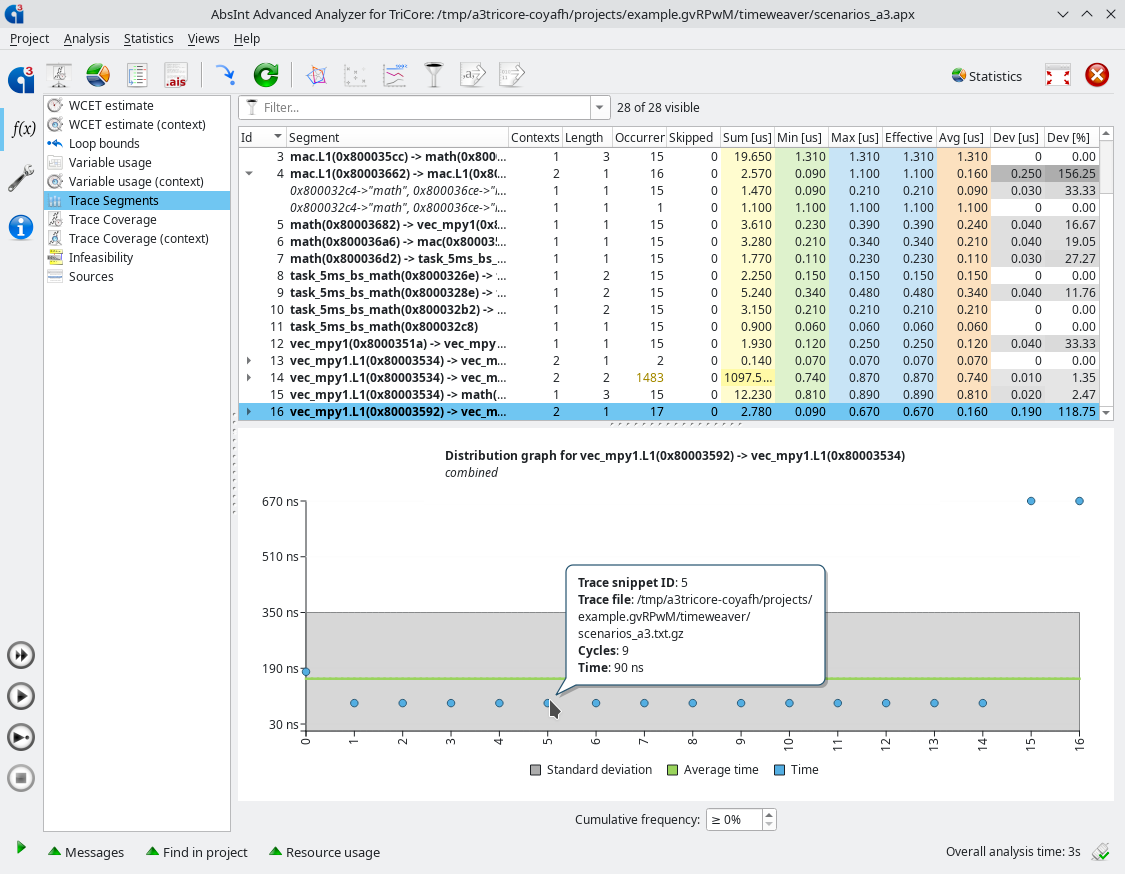

- The trace segment statistics view now shows data in time units instead of cycles if applicable.

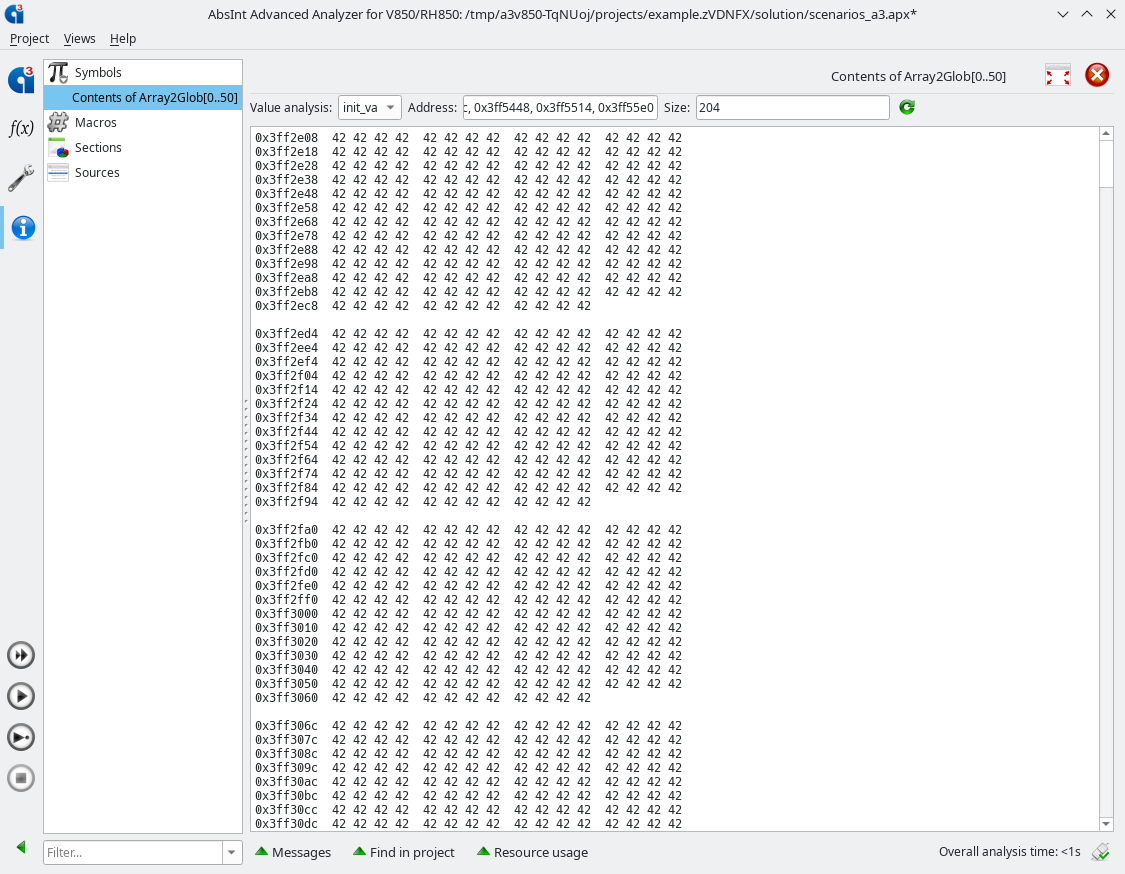

- Improved display of memory contents of multi-dimensional arrays in the Symbols view.

- Improved search of data in basic blocks in analysis result graphs.

Reporting

TimeWeaver now exports extended trace coverage information to XML report files. This information becomes available in a context-insensitive fashion by enabling “Output call graph”, and in a context-sensitive fashion by enabling “Show per context info” under “Setup" → “Reporting". The trace coverage can then be found in the XML report under a3 → timeweaver_analysis_task → timeweaver_analysis_results → trace_coverage.

Annotations

- Improved handling of complex area annotations that are used to define global register contents.

- Improved handling of the annotation scopes for

instruction snippet { … }andinstruction target { … }. - Improved handling of the functors

entriesandmem. - Improved handling of suppressed messages.

- Annotations such as

area .. writable: false;

now have an effect on annotations that read from (initially) writable memory.

Known issue

For code snippets annotated with evaluated as

and containing a loop or routine annotated with takes,

under certain circumstances the takes annotation

may be ignored by the analysis.

This issue is fixed in release 25.04.

If you cannot upgrade your software installation for any reason, please contact support@absint.com to receive a more detailed problem description, code examples, and known workarounds.

Value analysis

- Faster type domain analysis.

- More precise address computation for memory accesses.

ARM

- Improved switch-table decoding for Clang and DiabData.

C28x

- Support for the extended instruction sets

FINTDIV,TMU,FPU64, andVCRC. - Improved decoding of C28x ELF binaries.

M68020

- Support for the Microtec C compiler.

- Improved iterative decoding.

MIPS

- Improved iterative decoding.

PowerPC

- Now assuming that the value of the register

r2is given bySDA2BASEfor 32-bit executables and byTOCfor 64-bit executables. - Improved detection of mismatch between analysis and annotations.

- Improved iterative decoding.

RISC-V

- Improved automatic decoding of computed control-flow transitions.

RL78

- The target FLASH mirror area now has to be configured under Setup → Hardware.

TriCore

- Improved automatic decoding of syscall and trap control flow targets.

- Improved switch-table decoding for Clang.

V850/RH850

- Support for RH850G4MH instructions.

- Removed read classification for V850E3

stc.winstruction.

x86

- Added support for the

ENDBRANCHinstruction (part of the Intel Control Flow Enforcement Technology CET) which is treated like aNOP. - Improved iterative decoding.

Cache and pipeline analysis

- aiT for STM32F103xx now available (ARM Cortex-M3)

- WCET snippet-based validation now available for Am486.

TimeWeaver

- Support for V850/RH850.

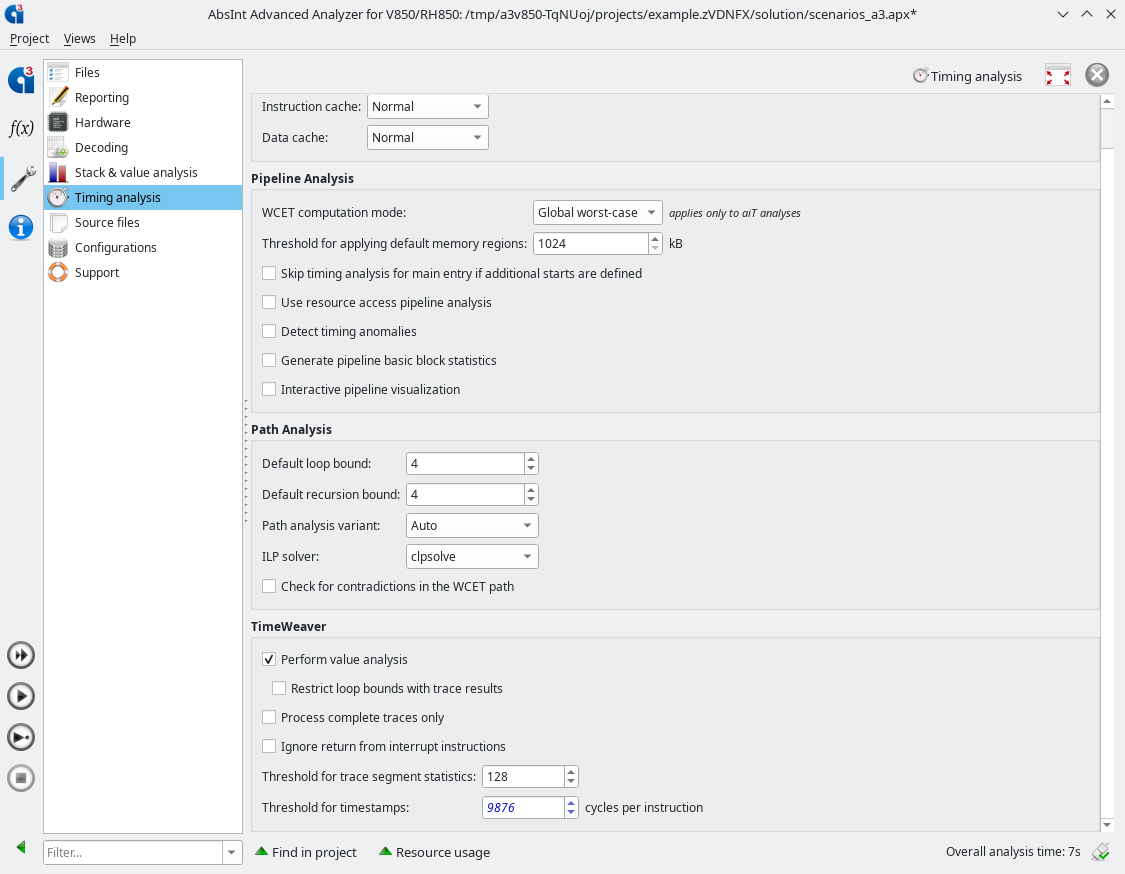

- Excessively high timestamps that might occur due to tracing errors can now be filtered out using the new GUI option “Threshold for timestamps” under “Setup” → “Timing analysis” → “TimeWeaver”. The default value is 6000 cycles per instruction.

- By default the analysis now tries to automatically determine the trace file format.

- The threshold for trace segment statistics is now applied per context.

- Trace segment statistics now show the full summary time spent in a segment where the segment threshold is applied.

- Trace segment statistics now keep track of the minimum and maximum time spent per trace segment.

- Introduced handling for OWNERSHIP information in Lauterbach traces.

- Improved detection of valid trace snippet end points.

TraceVisualizer

- Improved analysis performance for large traces and task sets.

- Improved handling of Lauterbach BRANCHFLOW traces.