Multiple analyses |

Improved Results Viewer |

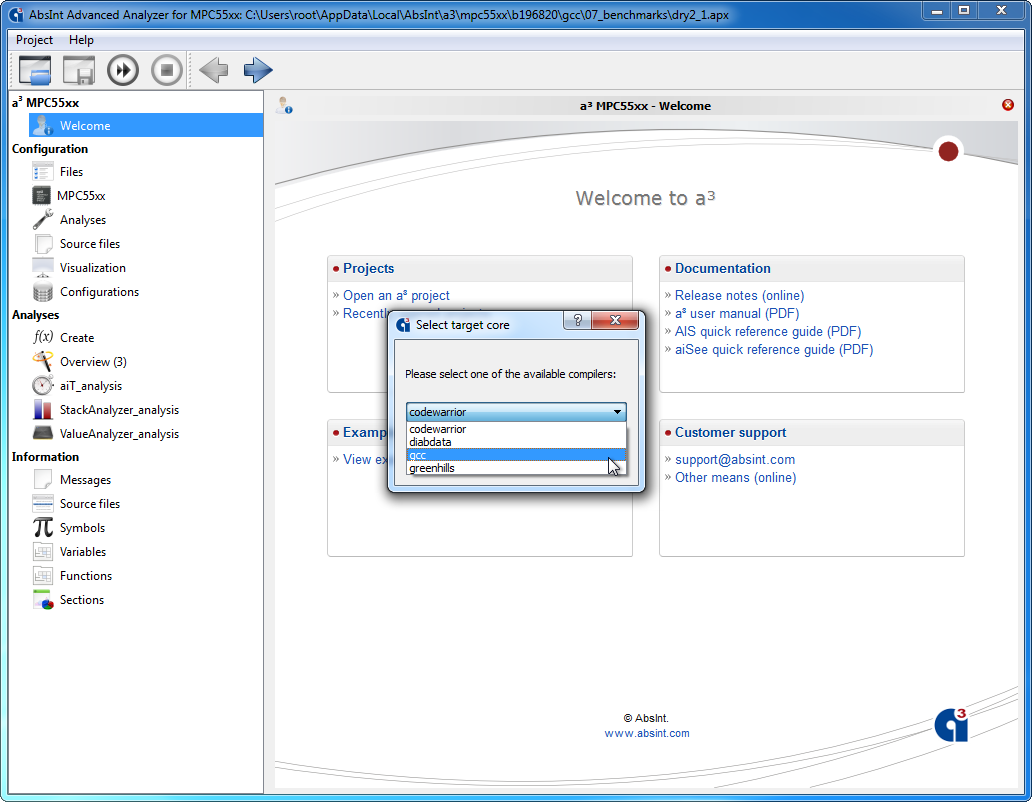

Improved compiler selection |

Targets

- a³ for C28x is now available, offering WCET analysis, stack usage analysis, and value analysis for TMS320F2808.

- aiT, StackAnalyzer and ValueAnalyzer for TriCore now support the 1197 and 1767 derivates.

- StackAnalyzer and ValueAnalyzer are now available for FR81S.

Qualification Support Kits (QSKs)

- Baseline information about the qualified tool is now consistently listed in TOR, VTP, and generated qualification run report.

- Qualifygui truncates report file before start of each qualification run.

- A definition of test case dependencies has been added to the VTP.

GUI

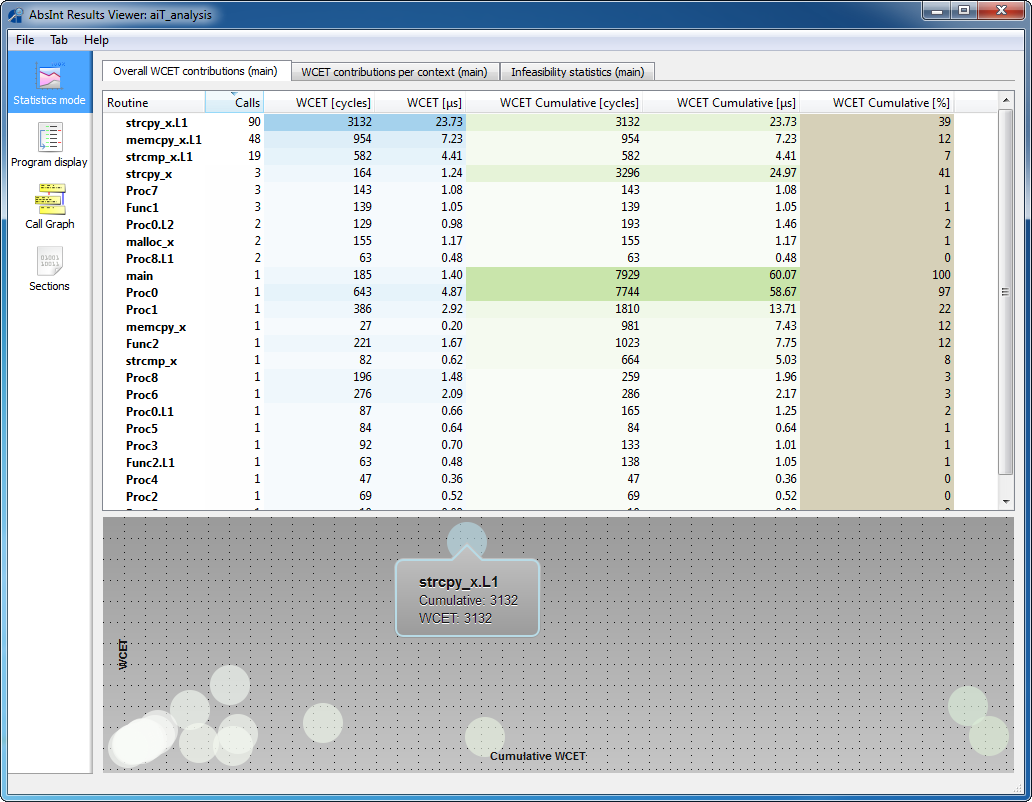

- Results Viewer now shows the number of times a function is called on the WCET path in the contributions table. See screenshot.

- Better message output for analysis with additional starts. Analysis steps for one additional start are grouped together with additional start name in header in message view.

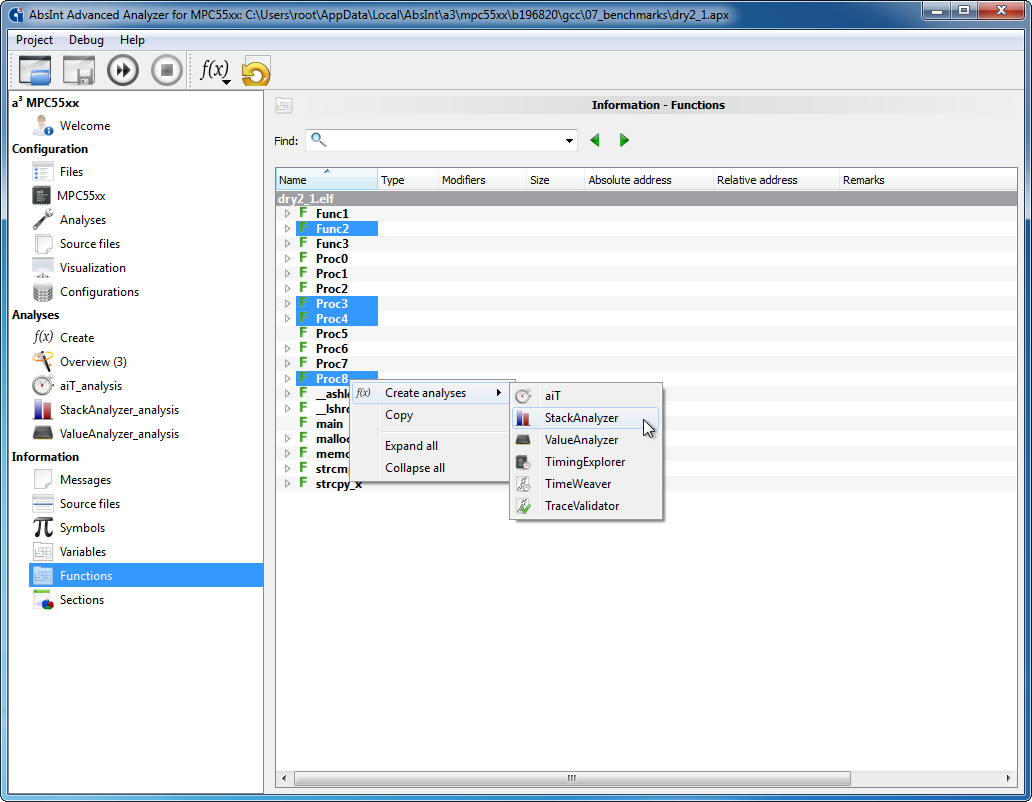

- It is now possible to create multiple analyses at once, from the Symbols or Functions views. See screenshot.

- The GUI highlights the exact location of an AIS parse error if possible.

- Now supporting XML report file for "Control Flow Visualizer".

- XTC: added support for additional aiT option

xml_style_sheet.

AIS

- It is now possible to modify register contents in speculative contexts

by means of an AIS2 annotation:

instruction <pp> enter|exit with speculatively: ... ;

- Access annotations for specific base registers are no longer supported. Examples:

global accesses restrict for base r10 to 0x1000..0x1fff; instruction 0x1000 accesses 0x1000..0x1fff for base r10;

Decoding

- Code duplication support for ARC, C33, H8, MPC5xx, MPC55xx, MPC56xx, PPC, TriCore, and x86.

- Improved support for delay slots.

- Delay slots will be code-duplicated for true and false edges (if not annulled) to allow for higher analysis precision.

- Improved decoding algorithm to reconstruct control flow graph.

- Improved decoding statistics:

- Loops no longer count as routines.

- Code-duplicated instructions are counted separately.

- Improved decoding if mixed branch/call to same routine occur.

- Improved "target is not analyzed" annotation.

- Improved diagnostic messages for conflicting AIS annotations: now linking to both AIS annotations in question.

- Improve loop type detection for architectures with delay slots or guarded execution.

- Added message numbers to output of unresolved computed calls and branches.

- Better handling of unresolved computed branches inside loops by loop transformation. They will now be included into the loop for better visualization.

- ARM:

- Added support for the ARM/Thumb VFPv3-D16 instruction set extension.

- Improved automatic resolving of switch tables (Thumb and GCC).

- C166: model traps as routine calls.

- C33: corrected memory sizes in AIS annotations.

- M68020:

- Fixed wrong decoding of the “DIVS.L <ea>, Dr:Dq” instruction. The wrong bits were extracted for the divisor operand, such that the extension word that is part of the divisor operand was erroneously decoded as an instruction of its own.

- Fixed missing distinction between “DIVS.L <ea>, Dq” and “DIVSL.L <ea>, Dr:Dq”.

- PPC: Support for HighTec GCC.

- Improved automatic resolving of switch tables (DiabData) and computed calls in general.

- Improve simplified mnemonics for VLE instructions.

- Support for extended PPC ISA sc/sync instructions, such as “sc 1”, “sync 1”, and “sync 2”.

- SPARC:

- Minor changes in assembly string for better readability.

trap_negativeis not interpreted as a function call anymore.

- TriCore: improved support for HighTec GCC.

- V850: support for HighTec GCC.

- x86: better support for GCC.

- The supported instruction set is that of the P5 architecture until the P54C implementation of Pentium, plus a few more modern instructions.

Stack and value analysis

- Improved StackAnalyzer precision by defaulting to

max-length = 2. - StackAnalyzer will compute the maximum usages for the individual stacks (e.g. user stack, system stack,…) separately.

- XML report for StackAnalyzer now contains additional information such as the stack layout of the architecture.

- Busy-waiting loops without volatile annotation found are no longer warnings.

- Speculative accesses for infeasible blocks now show up in the context-insensitive access information of the text and xml reports.

- Improved precision of feasibility check for the targets of conditional and computed control flow transitions, e.g. switch tables.

- Improved loop-bound diagnostic messages, now linking to the AIS annotations that have an effect on the loop in question.

- Improved precision of warnings issued by consistency checks for contents of memory cells annotated as constant.

- Improved error messages for stack modifying loops.

- Improved loop range computation.

- Improved error messages for contradictions of analyzed value with specified value, now including AIS annotation location.

- Improved comments about accessed symbols/variables in text report file.

- ARM:

- Improved stack analysis for GNU C/C++ compiler.

- Support ARM/Thumb VFPv3-D16 instruction set extension.

- C28x:

- A

[?]is printed to the report file instead of[X..Y] if Y-X >= 4*64k(i.e. the interval spans over 19 bits of address space). - The analyses themselves use the interval

[X..Y].

- A

- PPC: improved stack analysis if frame pointer is used by the compiler.

- TriCore: improved loop analysis.

- V850

- Improved loop analysis.

- Improved StackAnalyzer precision for GHS compiler.

- Improved branch splitting if addi is used as a compare instruction.

- x86

- The supported instruction set is that of the P5 architecture until the P54C implementation of Pentium, plus a few more modern instructions.

- Improve stack analysis precision for GCC compiled binaries (support frame pointer save + restore).

Cache and pipeline analysis

- Improved prevision of cache analysis in general.

- Improved detection of possible state explosions.

- aiT for MPC55xx, LEON2, MPC56xx, and MPC603e can now take cache-related preemption costs into account. This is done by the so-called Useful–Cache-Block analysis.

- C33: corrected pipeline behaviour for delay slots in slow memory.

- MPC603e: added support for e300 instruction fetch burst extension.

- MPC755s/PPC750/MPC603e/MPC7448s:

- Improved memory consumption of generic MCU model.

- Add support for different burst length values for SDR IC accesses.

- Implemented non-ECC. Implemented configurable ECC width (8, 16, 32, 64 bits).

- MPC7448(s): removed unsupported DRTRY Mode Option from GUI.

- TriCore TC1796: improved handling of stores to cached EBU memory.

- Tricore TC1797: improved analysis behavior in terms of memory consumption and computation time.

Visualization and reporting

- Execution count of routines on the WCET path is now exported to the XML report file as "count" attribute (global and per context).

- UCB analysis results are now exported to the XML report file.